# **AW-XH316**

# IEEE 802.11 a/b/g/n/ac/ax Wi-Fi

# + Bluetooth 5.2 Combo SIP Module

# **Datasheet**

Rev.A

DF

(For Standard)

#### **Features**

#### WiFi

- 802.11a/b/g/n/ac/ax compliant, dual-band capable (2.4/5 GHz).

- 5 GHz: 20/40/80-MHz channels, 1024-QAM, 2x2 MIMO providing up to 1.2 Gbps PHY data rate.

- 2.4 GHz: 20/40-MHz channels, 1024-QAM, 2x2 MIMO providing up to 574 Mbps PHY date rate.

- 802.11ax STA mode and Soft AP mode with 11ax scheduled access.

- Supports 802.11d, h, k, r, v, w, ai.

- Zero-wait dynamic frequency selection (DFS): Background channel availability check (CAC) scan for immediate switch to candidate DFS channel.

- On-chip power amplifiers and low-noise amplifiers.

- Supports multipoint external coexistence interface to optimize bandwidth utilization with other co-located wireless technologies such as LTE.

- Fast VSDB (Virtual Simultaneous Dual Band)

- Security:

- WPA, WAPI STA, WPA2 (Enterprise) and WPA3 (Enterprise) support for powerful encryption and authentication

- AES and TKIP in hardware for faster data encryption and IEEE 802.11i compatibility

- Reference WLAN subsystem provides Wi-Fi Protected Setup (WPS)

- Worldwide regulatory support: Global products supported with worldwide homologated design

- Integrated Arm® Cortex® R4 processor with tightly coupled memory for complete WLAN subsystem functionality. This architecture offloads the host processor completely from WLAN functionality.

#### **Bluetooth**

- Bluetooth 5.2 (BDR + EDR + BLE).

- All Bluetooth 5.0/5.1/5.2 optional features supported including LE-Audio.

- Dedicated Bluetooth RF path for best WLAN-BT coexistence performance.

- Bluetooth Class 1 or Class 2 transmitter operation.

- Supports extended synchronous connections (eSCO), for enhanced voice quality by allowing for retransmission of dropped packets.

- Adaptive frequency hopping (AFH) for reducing radio frequency interference.

- Interface support, host controller interface (HCI) using a high-speed UART interface and PCM/I2S for audio data.

- Supports multiple simultaneous Advanced Audio Distribution.

- Profiles (A2DP) for stereo sound.

- On-chip memory includes 512 KB SRAM and 2 MB ROM.

## **Revision History**

Document NO: R2-1316-DST-01

| Version | Revision Date | DCN NO.   | Description     | Initials | Approved        |

|---------|---------------|-----------|-----------------|----------|-----------------|

| Α       | 2021/04/16    | DCN021583 | Initial Version | JM.Pang  | Chihhao<br>Liao |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

|         |               |           |                 |          |                 |

## **Table of Contents**

| Features                              | 錯誤! | 尚未定義書籤。 |

|---------------------------------------|-----|---------|

| Revision History                      |     | 3       |

| Table of Contents                     |     | 4       |

| 1. Introduction                       |     | 5       |

| 1.1 Product Overview                  |     | 5       |

| 1.2 Block Diagram                     |     | 5       |

| 1.3 Specifications Table              |     | 6       |

| 1.3.1 General                         |     | 6       |

| 1.3.2 WLAN                            |     | 6       |

| 1.3.3 Bluetooth                       |     | 8       |

| 1.3.4 Operating Conditions            |     | 9       |

| 2. Pin Definition                     |     | 10      |

| 2.1 Pin Map                           |     | 10      |

| 2.2 Pin Table                         |     | 11      |

| 3. Electrical Characteristics         |     | 17      |

| 3.1 Absolute Maximum Ratings          |     | 18      |

| 3.2 Recommended Operating Conditions  |     | 18      |

| 3.3 Digital IO Pin DC Characteristics |     | 18      |

| 3.4 Host Interface                    |     | 19      |

| 3.4.1 SDIO Interface                  |     | 19      |

| 3.4.2 UART Interface                  |     | 22      |

| 3.4.3 PCIe Interface                  |     | 24      |

| 3.5 Power up Timing Sequence          |     | 25      |

| 3.6 Power Consumption*                |     | 29      |

| 3.6.1 WLAN                            |     | 29      |

| 3.6.2 Bluetooth                       |     | 29      |

| 4. Mechanical Information             |     | 30      |

| 4.1 Mechanical Drawing                |     | 30      |

| 5. Packaging Information              |     | 31      |

#### 1. Introduction

#### 1.1 Product Overview

The AW-XH316 module provides the highest level of integration for Commercial and Consumer systems, with integrated IEEE 802.11 a/b/g/n/ac/ax MAC/baseband/radio (dual-core 2×2 MIMO), Bluetooth 5.2+ Isochronous. It provides a small form-factor solution with minimal external components to drive down cost and allows for platform design flexibility in size, form, and function.

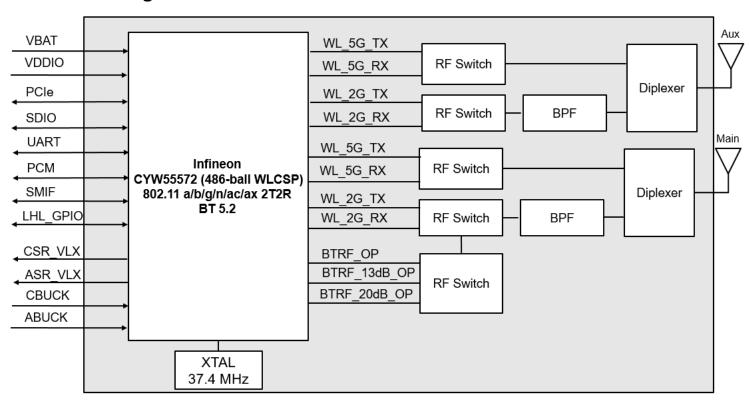

### 1.2 Block Diagram

AW-XH316 Block Diagram

## 1.3 Specifications Table

## 1.3.1 General

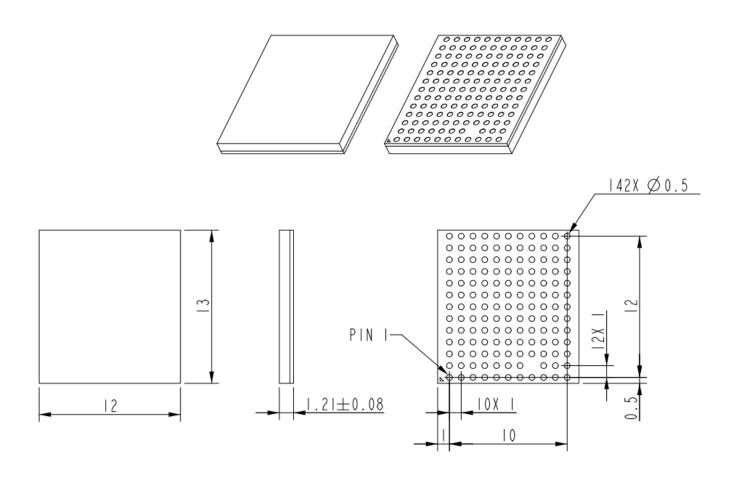

| Features            | Description                                                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Product Description | IEEE 802.11 a/b/g/n/ac/ax Wi-Fi + Bluetooth 5.2 Combo SIP Module                                                                           |

| Major Chipset       | Infineon CYW55572 (486-ball WLCSP)                                                                                                         |

| Host Interface      | WiFi + BT  ■ SDIO + UART  ■ PCIe + UART  Note: Please refer to G10 pin of 2.3 Host configuration interface table for your interface choice |

| Dimension           | 12mm x 13mm x 1.21mm                                                                                                                       |

| Form factor         | Sip module,142 pins                                                                                                                        |

| Antenna             | 2T2R, external ANT1(Main): WiFi/Bluetooth → TX/RX ANT2(Aux): WiFi → TX/RX                                                                  |

| Weight              | TBD                                                                                                                                        |

### 1.3.2 WLAN

| Features           | Description                                                                                                                                                                                    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLAN Standard      | IEEE 802.11 a/b/g/n/ac/ax 2T2R                                                                                                                                                                 |

| WLAN VID/PID       | N/A                                                                                                                                                                                            |

| WLAN SVID/SPID     | N/A                                                                                                                                                                                            |

| Frequency Rage     | WLAN: 2.4 GHz / 5GHz Band                                                                                                                                                                      |

| Modulation         | DSSS DBPSK(1Mbps), DQPSK(2Mbps), CCK(11/5.5Mbps) OFDM BPSK(9/6Mbps/MCS0), QPSK(18/12Mbps/MCS1~2), 16-QAM(36/24Mbps/MCS3~4), 64-QAM(72.2/54/48Mbps/MCS5~7), 256-QAM(MCS8~9), 1024-QAM(MCS10~11) |

| Number of Channels | 802.11b:<br>USA, Canada and Taiwan — 1 ~ 11                                                                                                                                                    |

|                      | NA 15                            | 4 4.5                            |             |            |               |  |  |

|----------------------|----------------------------------|----------------------------------|-------------|------------|---------------|--|--|

|                      | Most European Countries – 1 ~ 13 |                                  |             |            |               |  |  |

|                      | Japan - 1 ~ 13                   |                                  |             |            |               |  |  |

|                      | 802.11g:                         |                                  |             |            |               |  |  |

|                      | USA and Canada – 1 ~             | USA and Canada – 1 ~ 11          |             |            |               |  |  |

|                      | Most European Countrie           | Most European Countries − 1 ~ 13 |             |            |               |  |  |

|                      | 802.11n:                         |                                  |             |            |               |  |  |

|                      | USA and Canada – 1 ~             | 11                               |             |            |               |  |  |

|                      | Most European Countrie           |                                  |             |            |               |  |  |

|                      | 802.11a:                         | 33 – 1 ~ 10                      |             |            |               |  |  |

|                      |                                  | 2 50 00 0                        | 4 400 404   | 400 440    | 440 400       |  |  |

|                      | USA – 36, 40, 44, 48, 52         |                                  |             |            | 116, 120,     |  |  |

|                      | 124, 128, 132, 136, 140          | , 149, 153,                      | 157, 161, 1 | 165        |               |  |  |

|                      | 2.4G                             |                                  |             |            |               |  |  |

|                      |                                  | Min                              | Тур         | Max        | Unit          |  |  |

|                      | 11b (11Mbps)                     |                                  |             |            |               |  |  |

|                      | @EVM<35%                         | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      | 11g (54Mbps)                     |                                  |             |            |               |  |  |

|                      | @EVM≦-27 dB                      | <sub>IB</sub> TBD                | TBD         | TBD        | dBm           |  |  |

|                      | 11n (HT20 MCS7)                  |                                  |             |            |               |  |  |

|                      | @EVM≦-28 dB                      | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      |                                  |                                  |             |            |               |  |  |

|                      | 11n (HT40 MCS7)                  | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      | @EVM≦-28 dB                      |                                  |             | <b>0.2</b> |               |  |  |

|                      | 5G                               |                                  |             |            |               |  |  |

|                      |                                  | Min                              | Тур         | Max        | Unit          |  |  |

| Output Power         | 11a (54Mbps)                     | 101111                           | . , , ,     | Wich       | O T III       |  |  |

| Output i owei        | 11a (54Mbps)<br>    @EVM≦-25 dB  | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      | 11n (HT20 MCS7)                  |                                  |             |            |               |  |  |

|                      | 11 ,                             | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      | @EVM≦-27 dB                      |                                  |             |            |               |  |  |

|                      | 11n (HT40 MCS7)                  | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      | @EVM≦-27 dB                      | . 55                             | . 55        | 100        | <b>45</b> 111 |  |  |

|                      | 11ac (VHT20 MCS8)                | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      | @EVM≦-30 dB                      | טסו                              | טפו         | IDD        | UDIII         |  |  |

|                      | 11ac (VHT40 MCS9)                | TDD                              | TDD         | TDD        | ID.           |  |  |

|                      | @EVM≤-32 dB                      | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      | 11ac (VHT80 MCS9)                |                                  |             |            |               |  |  |

|                      | @EVM≦-32 dB                      | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      |                                  |                                  |             |            |               |  |  |

|                      | 11ax (HE80 MCS11)                | TBD                              | TBD         | TBD        | dBm           |  |  |

|                      | @EVM≦-35 dB                      |                                  |             |            |               |  |  |

|                      | 2.4G                             | T                                | <u> </u>    | 1 '        |               |  |  |

|                      |                                  | Min                              | Тур         | Max        | Unit          |  |  |

| Receiver Sensitivity | 11b (11Mbps)                     |                                  | TBD         | TBD        | dBm           |  |  |

|                      | 11g (54Mbps)                     |                                  | TBD         | TBD        | dBm           |  |  |

|                      | 11n (HT20 MCS7)                  |                                  | TBD         | TBD        | dBm           |  |  |

|                      | •                                | •                                | •           |            |               |  |  |

|           | 11n (HT40 MCS7)                                                                                                                                                                                                                                  |                                          | TBD | TBD          | dBm  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|--------------|------|

|           |                                                                                                                                                                                                                                                  |                                          |     |              |      |

|           | 5G(n/ac packets with                                                                                                                                                                                                                             | LDPC)                                    |     |              |      |

|           |                                                                                                                                                                                                                                                  | Min                                      | Тур | Max          | Unit |

|           | 11a (54Mbps)                                                                                                                                                                                                                                     |                                          | TBD | TBD          | dBm  |

|           | 11n (HT20 MCS7)                                                                                                                                                                                                                                  |                                          | TBD | TBD          | dBm  |

|           | 11n (HT40 MCS7)                                                                                                                                                                                                                                  |                                          | TBD | TBD          | dBm  |

|           | 11ac (VHT20 MCS8)                                                                                                                                                                                                                                |                                          | TBD | TBD          | dBm  |

|           | 11ac (VHT40 MCS9)                                                                                                                                                                                                                                |                                          | TBD | TBD          | dBm  |

|           | 11ac (VHT80 MCS9)                                                                                                                                                                                                                                |                                          | TBD | TBD          | dBm  |

|           | 11ax (HE80 MCS11)                                                                                                                                                                                                                                |                                          | TBD | TBD          | dBm  |

| Data Rate | 802.11b: 1, 2, 5.5, 11Mbps<br>802.11g: 6, 9, 12, 18, 24, 36, 48, 54Mbps<br>802.11n: MCS0~7 HT20/HT40<br>802.11a: 6, 9, 12, 18, 24, 36, 48, 54Mbps<br>802.11ac: MCS0~8 VHT20<br>802.11ac: MCS0~9 VHT40/VHT80<br>802.11ax: MCS10~11 HE20/HE40/HE80 |                                          |     |              |      |

| Security  | <ul> <li>WEP</li> <li>WPA/WPA2/WPA</li> <li>WMM, WMM-PS (</li> <li>AES (hardware ac</li> <li>TKIP (hardware su</li> <li>CKIP (software su</li> </ul>                                                                                             | U-APSD), V<br>celerator),<br>ccelerator) |     | t encryption | n    |

<sup>\*</sup> If you have any certification questions about output power please contact FAE directly

### 1.3.3 Bluetooth

| Features             | Description                                      |     |     |     |      |

|----------------------|--------------------------------------------------|-----|-----|-----|------|

| Bluetooth Standard   | Bluetooth 5.2                                    |     |     |     |      |

| Bluetooth VID/PID    | N/A                                              | N/A |     |     |      |

| Frequency Rage       | 2400~2483.5MHz                                   |     |     |     |      |

| Modulation           | GFSK (1Mbps), Π/4DQPSK (2Mbps) and 8DPSK (3Mbps) |     |     |     |      |

|                      |                                                  | Min | Тур | Max | Unit |

| Output Bower         | BDR                                              | TBD | TBD | TBD | dBm  |

| Output Power         | EDR                                              | TBD | TBD | TBD | dBm  |

|                      | Low Energy (2MHz)                                | TBD | TBD | TBD | dBm  |

|                      |                                                  | Min | Тур | Max | Unit |

| Receiver Sensitivity | BDR                                              | TBD | TBD | TBD | dBm  |

|                      | EDR                                              | TBD | TBD | TBD | dBm  |

| Low Energy (2MHz) | TBD | TBD | TBD | dBm |

|-------------------|-----|-----|-----|-----|

|                   |     |     |     |     |

## 1.3.4 Operating Conditions

| Features              | Description          |  |  |  |  |  |

|-----------------------|----------------------|--|--|--|--|--|

|                       | Operating Conditions |  |  |  |  |  |

| Voltage               | 3.3V                 |  |  |  |  |  |

| Operating Temperature | -40°C to 85°C        |  |  |  |  |  |

| Operating Humidity    | less than 85% R.H.   |  |  |  |  |  |

| Storage Temperature   | -40°C to 125°C       |  |  |  |  |  |

| Storage Humidity      | less than 60% R.H.   |  |  |  |  |  |

| ESD Protection        |                      |  |  |  |  |  |

| Human Body Model      | TBD                  |  |  |  |  |  |

| Changed Device Model  | TBD                  |  |  |  |  |  |

## 2. Pin Definition

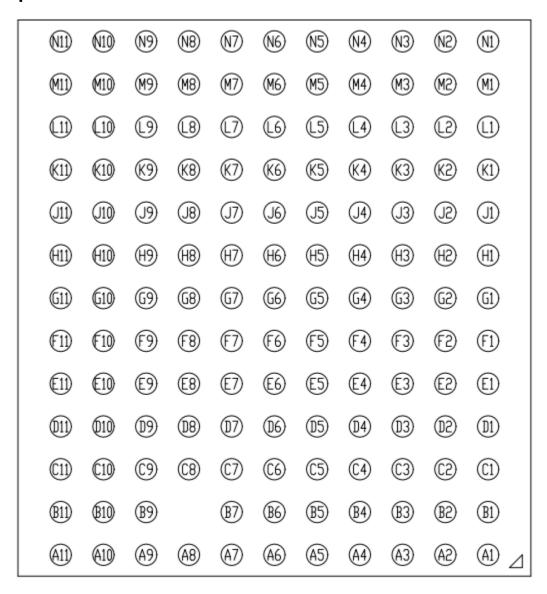

## 2.1 Pin Map

AW-XH316 Pin Map (Top View)

## 2.2 Pin Table

| Pin No    | Definition   | Basic Description                                                                                                                                                                                                                                                                  | Voltage | Туре |

|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| A1        | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| A2        | PCIE_RDN     | PCIE Receiver Differential Pair Negative Input                                                                                                                                                                                                                                     |         | I    |

| А3        | PCIE_RDP     | PCIE Receiver Differential Pair Positive Input                                                                                                                                                                                                                                     |         | I    |

| A4        | PCIE_TDN     | PCIE Transmitter Differential Pair Negative Output                                                                                                                                                                                                                                 |         | 0    |

| A5        | PCIE_TDP     | PCIE Transmitter Differential Pair Positive Output                                                                                                                                                                                                                                 |         | 0    |

| A6        | PCIE_REFCLKN | PCIE Differential Pair Clock Source (100 MHz) Negative Input.                                                                                                                                                                                                                      |         | I    |

| A7        | PCIE_REFCLKP | PCIE Differential Pair Clock Source (100 MHz) Positive Input.                                                                                                                                                                                                                      |         | 1    |

| <b>A8</b> | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| A9        | CSR_VLX      | CSR Power Stage Output to Inductor                                                                                                                                                                                                                                                 | 0.9V    | 0    |

| A10       | ASR_VLX      | ASR Power Stage Output to Inductor                                                                                                                                                                                                                                                 | 1.12V   | 0    |

| A11       | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| B1        | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| B2        | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| В3        | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| В4        | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| B5        | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| В6        | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| В7        | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| В9        | CSR_VLX      | CSR Power Stage Output to Inductor                                                                                                                                                                                                                                                 | 0.9V    | 0    |

| B10       | ASR_VLX      | ASR Power Stage Output to Inductor                                                                                                                                                                                                                                                 | 1.12V   | 0    |

| B11       | GND          | Ground.                                                                                                                                                                                                                                                                            |         | GND  |

| C1        | WL_REG_ON    | Used by the PMU to power up the WLAN section. It is also OR-gated with the BT_REG_ON input to control the internal CYW55572 regulators. When this pin is high, the regulators are enabled and the WLAN section is out of reset. When this pin is low the WLAN section is in reset. | VDDIO   | I    |

|            |               | If both the BT_REG_ON and WL_REG_ON pins are low,                                                                                                                                                                                                                                                  |       |     |

|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|

|            |               | the regulators are disabled.                                                                                                                                                                                                                                                                       |       |     |

| C2         | BT_PCM_IN     | PCM data input.                                                                                                                                                                                                                                                                                    | VDDIO | I   |

| C3         | BT_PCM_SYNC   | PCM sync; can be master (output) or slave (input), or SLIMbus data.                                                                                                                                                                                                                                | VDDIO | I/O |

| C4         | PCIE_CLKREQ_L | PCIe clock request signal which indicates when the REFCLK to the PCIe interface can be gated.  1 = the clock can be gated.  0 = the clock is required.                                                                                                                                             |       | OD  |

| <b>C</b> 5 | GND           | Ground.                                                                                                                                                                                                                                                                                            |       | GND |

| C6         | GND           | Ground.                                                                                                                                                                                                                                                                                            |       | GND |

| <b>C</b> 7 | BT_REG_ON     | Used by the PMU (OR-gated with WL_REG_ON) to power up the internal CYW55572 regulators. If both the BT_REG_ON and WL_REG_ON pins are low, the regulators are disabled. When this pin is low and WL_REG_ON is high, the BT section is in reset.                                                     | VDDIO | I   |

| C8         | GND           | Ground.                                                                                                                                                                                                                                                                                            |       | GND |

| <b>C</b> 9 | GND           | Ground.                                                                                                                                                                                                                                                                                            |       | GND |

| C10        | VBAT          | 3.3V power pin                                                                                                                                                                                                                                                                                     | 3.3V  | VCC |

| C11        | VBAT          | 3.3V power pin                                                                                                                                                                                                                                                                                     | 3.3V  | VCC |

| D1         | PCIE_PERST_L  | PCIe System Reset. This input is the PCIe reset as defined in the PCIe base specification v1.1                                                                                                                                                                                                     |       | I   |

| D2         | GND           | Ground.                                                                                                                                                                                                                                                                                            |       | GND |

| D3         | GND           | Ground.                                                                                                                                                                                                                                                                                            |       | GND |

| D4         | BT_PCM_OUT    | PCM data output.                                                                                                                                                                                                                                                                                   | VDDIO | Ο   |

| D5         | BT_PCM_CLK    | PCM clock; can be master (output) or slave (input).                                                                                                                                                                                                                                                | VDDIO | I/O |

| D6         | PCIE_PME_L    | PCI power management event output. Used to request a change in the device or system power state. The assertion and deassertion of this signal is asynchronous to the PCIe reference clock. This signal has an opendrain output structure, as per the PCI Bus Local Bus Specification, revision 2.3 |       | OD  |

| D7         | LHL_GPIO3     | Miscellaneous General Purpose I/O                                                                                                                                                                                                                                                                  | VDDIO | I/O |

| D8         | GND           | Ground.                                                                                                                                                                                                                                                                                            |       | GND |

| D9         | CBUCK_0P9     | Internal Buck 0.9V voltage generation pin.                                                                                                                                                                                                                                                         | 1.12V | I   |

| D10        |               |                                                                                                                                                                                                                                                                                                    |       |     |

| D11        | ABUCK_1P12              | Internal Buck 1.12V voltage generation pin.                                                             | 1.12V | I   |

|------------|-------------------------|---------------------------------------------------------------------------------------------------------|-------|-----|

| E1         | GPIO_0_WL_HOST<br>_WAKE | WL Host Wake.                                                                                           | VDDIO | 0   |

| E2         | GND                     | Ground.                                                                                                 |       | GND |

| E3         | BT_HOST_WAKE            | Bluetooth HOST_WAKE.                                                                                    | VDDIO | I/O |

| E4         | BT_CLK_REQ              | A Bluetooth clock request.                                                                              | VDDIO | I/O |

| E5         | GND                     | Ground.                                                                                                 |       | GND |

| <b>E</b> 6 | LHL_GPIO4               | Miscellaneous General Purpose I/O                                                                       | VDDIO | I/O |

| <b>E7</b>  | LPO_IN                  | External Sleep Clock Input (32.768 kHz)                                                                 |       | I   |

| E8         | GPIO_11_WL_UAR<br>T TX  | Debug UART Serial Output.                                                                               | VDDIO | 0   |

| E9         | GPIO_10_WL_UAR<br>T_RX  | Debug UART Serial Input.                                                                                | VDDIO | 1   |

| E10        | GND                     | Ground.                                                                                                 |       | GND |

| E11        | ABUCK_1P12              | Internal Buck 1.12V voltage generation pin.                                                             | 1.12V | I   |

| F1         | GND                     | Ground.                                                                                                 |       | GND |

| F2         | BT_DEV_WAKE             | Bluetooth DEVICE WAKE                                                                                   | VDDIO | I/O |

| F3         | BT_UART_TXD             | UART Serial Output. Serial data output for the HCI UART interface.                                      | VDDIO | 0   |

| F4         | BT_UART_RXD             | UART serial input. Serial data input for the HCI UART interface.                                        | VDDIO | I   |

| F5         | GND                     | Ground.                                                                                                 |       | GND |

| F6         | LHL_GPIO2               | Miscellaneous General Purpose I/O                                                                       | VDDIO | I/O |

| F7         | GND                     | Ground.                                                                                                 |       | GND |

| F8         | GND                     | Ground.                                                                                                 |       | GND |

| F9         | GND                     | Ground.                                                                                                 |       | GND |

| F10        | GND                     | Ground.                                                                                                 |       | GND |

| F11        | VDDIO                   | 1.8 V IO Supply for WLAN GPIOs                                                                          | VDDIO | VCC |

| G1         | GND                     | Ground.                                                                                                 |       | GND |

| G2         | BT_UART_RTS_N           | UART request-to-send. Active-low request-to-send signal for the HCI UART interface. BT LED control pin. | VDDIO | 0   |

| G3  | GND           | Ground.                                                                         |        | GND |

|-----|---------------|---------------------------------------------------------------------------------|--------|-----|

|     |               |                                                                                 | \/DC:0 |     |

| G4  | LHL_GPIO5     | Miscellaneous General Purpose I/O                                               | VDDIO  | I/O |

| G5  | BT_UART_CTS_N | UART clear-to-send. Active-low clear-to-send signal for the HCI UART interface. | VDDIO  | I   |

| G6  | LHL_GPIO0     | Miscellaneous General Purpose I/O                                               | VDDIO  | I/O |

| G7  | WL_DEV_WAKE   | WL DEV_WAKE.                                                                    | VDDIO  | I/O |

| G8  | GND           | Ground.                                                                         |        | GND |

| G9  | GND           | Ground.                                                                         |        | GND |

| G10 | GPIO_1        | Strap option                                                                    | VDDIO  | I/O |

| G11 | GND           | Ground.                                                                         |        | GND |

| H1  | GND           | Ground.                                                                         |        | GND |

| H2  | SDIO_CMD      | SDIO Command Line                                                               | VDDIO  | I/O |

| Н3  | SDIO_CLK      | SDIO Clock Input                                                                | VDDIO  | I   |

| H4  | GND           | Ground.                                                                         |        | GND |

| Н5  | GND           | Ground.                                                                         |        | GND |

| Н6  | GND           | Ground.                                                                         |        | GND |

| H7  | GND           | Ground.                                                                         |        | GND |

| Н8  | GND           | Ground.                                                                         |        | GND |

| Н9  | SMIF_SPHB_DQ3 | SMIF Data Line 3                                                                | VDDIO  | I/O |

| H10 | SMIF_SPHB_DQ1 | SMIF Data Line 1                                                                | VDDIO  | I/O |

| H11 | SMIF_SPHB_DQ2 | SMIF Data Line 0                                                                | VDDIO  | I/O |

| J1  | SDIO_DATA_0   | SDIO Data Line 0                                                                | VDDIO  | I/O |

| J2  | SDIO_DATA_3   | SDIO Data Line 3                                                                | VDDIO  | I/O |

| J3  | SDIO_DATA_2   | SDIO Data Line 2                                                                | VDDIO  | I/O |

| J4  | SDIO_DATA_1   | SDIO Data Line 1                                                                | VDDIO  | I/O |

| J5  | GND           | Ground.                                                                         |        | GND |

|     | 10.                 |                                       |       |          |

|-----|---------------------|---------------------------------------|-------|----------|

| J6  | GND                 | Ground.                               |       | GND      |

| J7  | GND                 | Ground.                               |       | GND      |

| J8  | GND                 | Ground.                               |       | GND      |

| J9  | SMIF_SPHB_CS0_<br>N | SMIF Chip Select0 Active-low Output   | VDDIO | 0        |

| J10 | SMIF_SPHB_CK        | SMIF Clock Output                     | VDDIO | 0        |

| J11 | SMIF_SPHB_DQ0       | SMIF Data Line 0                      | VDDIO | I/O      |

| K1  | GND                 | Ground.                               |       | GND      |

| K2  | GND                 | Ground.                               |       | GND      |

| К3  | BT_GPIO_11          | BT General Purpose I/O                | VDDIO | I/O      |

| K4  | GND                 | Ground.                               |       | GND      |

| K5  | GND                 | Ground.                               |       | GND      |

| K6  | GND                 | Ground.                               |       | GND      |

| K7  | GND                 | Ground.                               |       | GND      |

| K8  | GND                 | Ground.                               |       | GND      |

| K9  | GND                 | Ground.                               |       | GND      |

| K10 | GND                 | Ground.                               |       | GND      |

| K11 | GND                 | Ground.                               |       | GND      |

| L1  | NC                  | Floating Pin, No connect to anything. |       | Floating |

| L2  | GND                 | Ground.                               |       | GND      |

| L3  | GND                 | Ground.                               |       | GND      |

| L4  | GND                 | Ground.                               |       | GND      |

| L5  | GND                 | Ground.                               |       | GND      |

| L6  | GND                 | Ground.                               |       | GND      |

| L7  | GND                 | Ground.                               |       | GND      |

| L8  | GND                 | Ground.                               |       | GND      |

| <b>L9</b> GI  | ND    | Ground.                     | GND |

|---------------|-------|-----------------------------|-----|

| <b>L10</b> GI | ND    | Ground.                     | GND |

| <b>L11</b> GI | ND    | Ground.                     | GND |

| M1 GI         | ND    | Ground.                     | GND |

| M2 GI         | ND    | Ground.                     | GND |

| M3 GI         | ND    | Ground.                     | GND |

| M4 GI         | ND    | Ground.                     | GND |

| M5 GI         | ND    | Ground.                     | GND |

| M6 GI         | ND    | Ground.                     | GND |

| M7 GI         | ND    | Ground.                     | GND |

| M8 GI         | ND    | Ground.                     | GND |

| <b>M9</b> GI  | ND    | Ground.                     | GND |

| <b>M10</b> GI | ND    | Ground.                     | GND |

| <b>M11</b> GI | ND    | Ground.                     | GND |

| N1 C          | 0_ANT | WLAN/BT Main RF TX/RX path. | RF  |

| N2 GI         | ND    | Ground.                     | GND |

| N3 GI         | ND    | Ground.                     | GND |

| N4 GI         | ND    | Ground.                     | GND |

| <b>N5</b> GI  | ND    | Ground.                     | GND |

| N6 GI         | ND    | Ground.                     | GND |

| N7 GI         | ND    | Ground.                     | GND |

| <b>N8</b> C   | 1_ANT | WLAN/BT Aux RF TX/RX path.  | RF  |

| N9 GI         | ND    | Ground.                     | GND |

| <b>N10</b> GI | ND    | Ground.                     | GND |

| <b>N11</b> GI | ND    | Ground.                     | GND |

## 2.3 Host Configuration Interface Table

| Pin No       | Definition | Interface | Strap |

|--------------|------------|-----------|-------|

| G10 GPIO_1 - | PCIE       | 1         |       |

|              | GFIO_I     | SDIO      | 0     |

## 3. Electrical Characteristics

## 3.1 Absolute Maximum Ratings

| Symbol | Parameter                                         | Minimum | Typical | Maximum | Unit |

|--------|---------------------------------------------------|---------|---------|---------|------|

| VBAT   | DC supply for the<br>VBAT and PA driver<br>supply | -0.5    | -       | 6.0     | V    |

| VDDIO  | DC supply voltage for digital I/O                 | -0.5    | -       | 2.2     | V    |

| Tj     | Maximum junction temperature                      | -       | -       | 125     | °C   |

## 3.2 Recommended Operating Conditions

| S | ymbol | Parameter                              | Minimum | Typical | Maximum | Unit |

|---|-------|----------------------------------------|---------|---------|---------|------|

| \ | VBAT  | Power supply for<br>Internal Regulator | 3.0     | 3.3     | 4.8     | ٧    |

| V | /DDIO | DC supply voltage for digital I/O      | 1.71    | 1.8     | 1.89    | V    |

## 3.3 Digital IO Pin DC Characteristics

| Symbol                       | Parameter           | Minimum      | Typical | Maximum         | Unit |  |

|------------------------------|---------------------|--------------|---------|-----------------|------|--|

| Digital I/O pins, VDDIO=1.8V |                     |              |         |                 |      |  |

| ViH                          | Input high voltage  | 0.65 × VDDIO | -       | -               | V    |  |

| VIL                          | Input low voltage   | -            | -       | 0.35 ×<br>VDDIO | V    |  |

| Vон                          | Output high voltage | VDDIO – 0.45 | -       | -               | V    |  |

| V <sub>OL</sub>              | Output Low Voltage  | -            | -       | 0.45            | V    |  |

#### 3.4 Host Interface

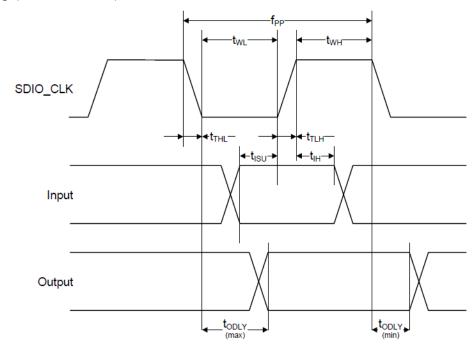

### 3.4.1 SDIO Interface

SDIO Bus Timing (Default Mode)

SDIO Bus Timing Parameters (Default Mode)

| Parameter                              | Symbol                                                            | Minimum | Typical | Maximum | Unit |  |  |  |

|----------------------------------------|-------------------------------------------------------------------|---------|---------|---------|------|--|--|--|

| SDIO CLK (All values are referred to n | SDIO CLK (All values are referred to minimum VIH and maximum VIL) |         |         |         |      |  |  |  |

| Frequency – Data Transfer mode         | f <sub>PP</sub>                                                   | 0       | _       | 25      | MHz  |  |  |  |

| Frequency – Identification mode        | fod                                                               | 0       | _       | 400     | kHz  |  |  |  |

| Clock low time                         | tw∟                                                               | 10      | _       | _       | ns   |  |  |  |

| Clock high time                        | twн                                                               | 10      | _       | _       | ns   |  |  |  |

| Clock rise time                        | tтьн                                                              | _       | _       | 10      | ns   |  |  |  |

| Clock low time                         | tтнL                                                              | _       | _       | 10      | ns   |  |  |  |

| Inputs: CMD, DAT (referenced to CLK)   |                                                                   |         |         |         |      |  |  |  |

| Input setup time                       | tısu                                                              | 5       | _       | _       | ns   |  |  |  |

| Input hold time                        | tıн                                                               | 5       | _       | _       | ns   |  |  |  |

| Outputs: CMD, DAT (referenced to CLK)  |                                                                   |         |         |         |      |  |  |  |

| Output delay time – Data Transfer mode | todly | 0 | _ | 14 | ns |

|----------------------------------------|-------|---|---|----|----|

| Output delay time – Identification     | todly | 0 | _ | 50 | ns |

| mode                                   |       | _ |   |    |    |

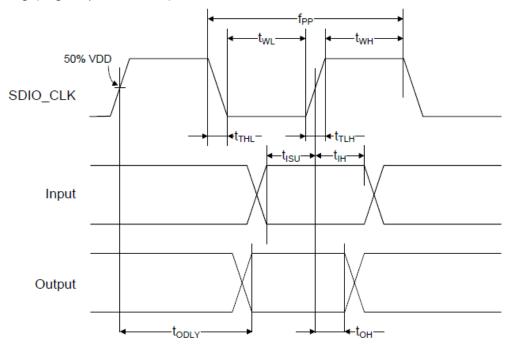

## SDIO Bus Timing (High-Speed Mode)

SDIO Bus Timing Parameters (High-Speed Mode)

| Parameter                                                                       | Symbol          | Minimum | Typical | Maximum | Unit |  |  |

|---------------------------------------------------------------------------------|-----------------|---------|---------|---------|------|--|--|

| SDIO CLK (all values are referred to minimum VIH and maximum VIL <sup>b</sup> ) |                 |         |         |         |      |  |  |

| Frequency – Data Transfer Mode                                                  | f <sub>PP</sub> | 0       | _       | 50      | MHz  |  |  |

| Frequency - Identification Mode                                                 | fod             | 0       | _       | 400     | kHz  |  |  |

| Clock low time                                                                  | tw∟             | 7       | _       | _       | ns   |  |  |

| Clock high time                                                                 | twн             | 7       | _       | _       | ns   |  |  |

| Clock rise time                                                                 | tтьн            | _       | _       | 3       | ns   |  |  |

| Clock low time                                                                  | tтнL            | _       | _       | 3       | ns   |  |  |

| Inputs: CMD, DAT (referenced to CLK)                                            |                 |         |         |         |      |  |  |

| Input setup Time                                                                | tısu            | 6       | _       | _       | ns   |  |  |

| Input hold Time                                                                 | tıн             | 2       | _       | _       | ns   |  |  |

| Outputs: CMD, DAT (referenced to CLK)                                           |                 |         |         |         |      |  |  |

| Output delay time – Data Transfer<br>Mode | todly | _   | _ | 14 | ns |

|-------------------------------------------|-------|-----|---|----|----|

| Output hold time                          | tон   | 2.5 | _ | 1  | ns |

| Total system capacitance (each line)      | CL    | _   | _ | 40 | pF |

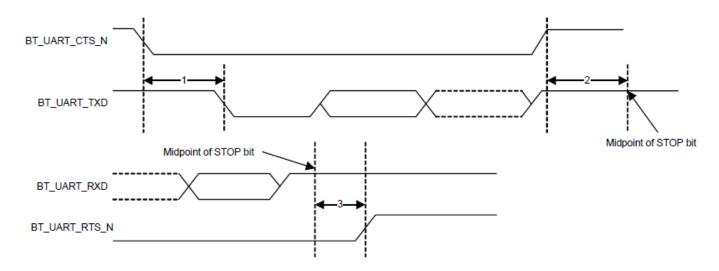

#### 3.4.2 UART Interface

The AW-XH316 UART is a standard 4-wire interface (RX, TX, RTS, and CTS) with adjustable baud rates from 9600 bps to 4.0 Mbps. The baud rate may be selected through a vendor-specific UART HCI command.

UART has a 1040-byte receive FIFO and a 1040-byte transmit FIFO to support EDR. Access to the FIFOs is conducted through the AHB interface through either DMA/CPU. The UART supports the Bluetooth 5.0 UART HCI specification. The default baud rate is 115.2 Kbaud.

The AW-XH316 UART can perform XON/XOFF flow control and includes hardware support for the Serial Line Input Protocol (SLIP). It can also perform wake-on activity. For example, activity on the RX or CTS inputs can wake the chip from a sleep state.

Normally, the UART baud rate is set by a configuration record downloaded after device reset and the host does not need to adjust the baud rate. Support for changing the baud rate during normal HCI UART operation is included through a vendor-specific command that allows the host to adjust the contents of the baud rate registers. The AW-XH316 UARTs operate correctly with the host UART as long as the combined baud rate error of the two devices is within ±2%.

**UART Interface Signals**

| PIN No. | Name          | Description                                                                                  | Туре |

|---------|---------------|----------------------------------------------------------------------------------------------|------|

| F3      | BT_UART_TXD   | Bluetooth UART Serial Output. Serial data output for the HCI UART Interface                  | 0    |

| F4      | BT_UART_RXD   | Bluetooth UART Series Input. Serial data input for the HCI UART Interface                    | I    |

| G2      | BT_UART_RTS_N | Bluetooth UART Request-to-Send. Active-low request-to-send signal for the HCI UART interface | 0    |

| G5      | BT_UART_CTS_N | Bluetooth UART Clear-to-Send. Active-low clear-to-send signal for the HCI UART interface.    | I    |

### **UART Timing**

|   | Reference Characteristics                                  | Minimum | Typical | Maximum | Unit        |

|---|------------------------------------------------------------|---------|---------|---------|-------------|

| 1 | Delay time, BT_UART_CTS_N low to BT_UART_TXD valid         | _       | _       | 1.5     | Bit periods |

| 2 | Setup time, BT_UART_CTS_N high before midpoint of stop bit | _       | _       | 0.5     | Bit periods |

| 3 | Delay time, midpoint of stop bit to BT_UART_RTS_N high     | _       | _       | 0.5     | Bit periods |

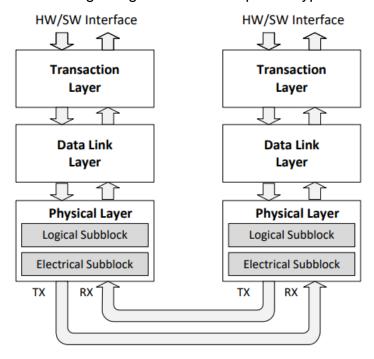

#### 3.4.3 PCIe Interface

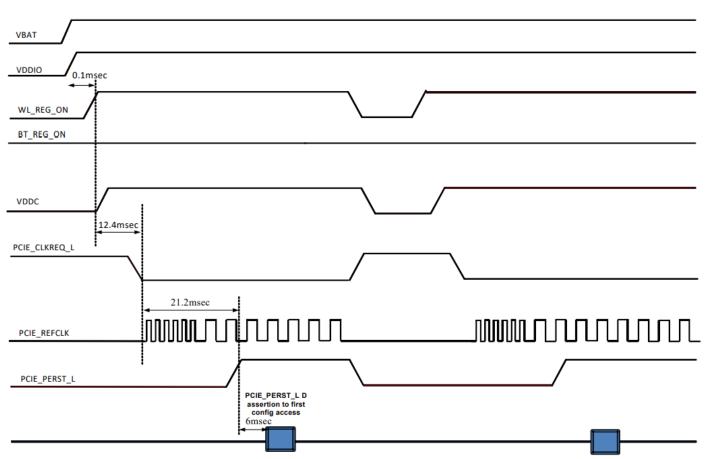

The PCI Express (PCIe) core in AW-XH316 is a high-performance serial I/O interconnect that is protocol compliant and electrically compatible with the PCI Express Base Specification v3.0 running at Gen2 speeds. This core contains all the necessary blocks, including logical and electrical functional sub blocks to perform PCIe functionality and maintain high-speed links, using existing PCI system configuration software implementations without modification.

Organization of the PCIe core is in logical layers: Transaction Layer, Data Link Layer, and Physical Layer, as shown in Figure 20. A configuration or link management block is provided for enumerating the PCIe configuration space and supporting generation and reception of System Management Messages by communicating with PCIe layers.

Each layer is partitioned into dedicated transmit and receive units that allow point-to-point communication between the host and AW-XH316 device. The transmit side processes outbound packets whereas the receive side processes inbound packets. Packets are formed and generated in the Transaction and Data Link Layer for transmission onto the high-speed links and onto the receiving device. A header is added at the beginning to indicate the packet type and any other optional fields.

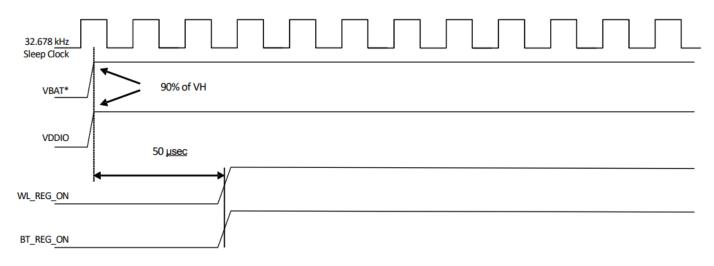

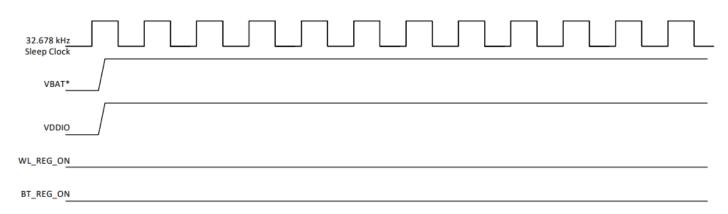

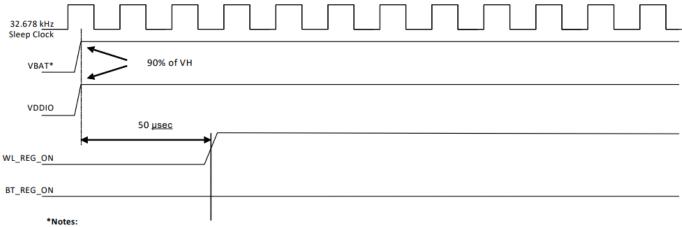

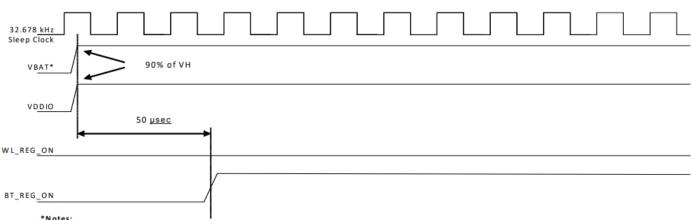

## 3.5 Power up Timing Sequence

AW-XH316 has two signals that allow the host to control power consumption by enabling or disabling the Bluetooth, WLAN, and internal regulator blocks. These signals are described below. Additionally, diagrams are provided to indicate proper sequencing of the signals for various operational states. The timing values indicated are minimum required values; longer delays are also acceptable.

#### **Description of Control Signals**

- WL\_REG\_ON: Used by the PMU to power up the WLAN section. It is also OR-gated with the BT\_REG\_ON input to control the internal AW-XH316 regulators. When this pin is high, the regulators are enabled and the WLAN section is out of reset. When this pin is low the WLAN section is in reset. If both the BT\_REG\_ON and WL\_REG\_ON pins are low, the regulators are disabled.

- BT\_REG\_ON: Used by the PMU (OR-gated with WL\_REG\_ON) to power up the internal AW-XH316 regulators. If both the BT\_REG\_ON and WL\_REG\_ON pins are low, the regulators are disabled. When this pin is low and WL\_REG\_ON is high, the BT section is in reset.

#### **Note**

- AW-XH316 has an internal power-on reset (POR) circuit. The device will be held in reset for a maximum of 110 ms after VDDC and VDDIO have both passed the POR threshold. Wait at least 150 ms after VDDC and VDDIO are available before initiating PCIe accesses.

- VBAT and VDDIO should not rise 10%–90% faster than 40 microseconds.

#### \*Notes:

- 1. VBAT and VDDIO should not rise 10%-90% faster than 40 microseconds.

- 2. VBAT should be up before or at the same time as VDDIO. VDDIO should NOT be present first or be held high before VBAT is high.

#### WLAN = ON, Bluetooth = ON

#### \*Notes:

- 1. VBAT and VDDIO should not rise 10%-90% faster than 40 microseconds.

- 2. VBAT should be up before or at the same time as VDDIO. VDDIO should NOT be present first or be held high before VBAT is high.

#### WLAN = OFF, Bluetooth = OFF

- 1. VBAT and VDDIO should not rise 10%-90% faster than 40 microseconds.

- 2. VBAT should be up before or at the same time as VDDIO. VDDIO should NOT be present first or be held high before VBAT is high.

### WLAN = ON, Bluetooth = OFF

1. VBAT and VDDIO should not rise 10%–90% faster than 40 microseconds.

2. VBAT should be up before or at the same time as VDDIO. VDDIO should NOT be present first or be held high before VBAT is high.

#### WLAN = OFF, Bluetooth = ON

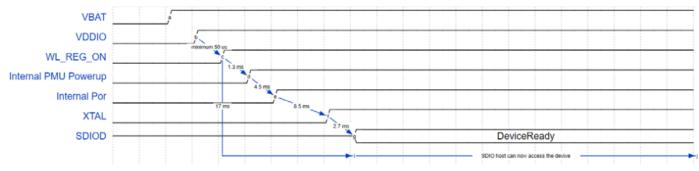

SDIO host can access device after 17ms from assertion WL\_REG\_ON

### **WLAN Boot-Up Sequence for SDIO Host**

There is variation of about +/-30% on above timing numbers

### **WLAN Power-Up Sequence for PCIe Host**

## 3.6 Power Consumption\*

#### 3.6.1 WLAN

#### **TBD**

\* The power consumption is based on Azurewave test environment, these data for reference only.

#### 3.6.2 Bluetooth

#### **TBD**

\* The power consumption is based on Azurewave test environment, these data for reference only.

## 4. Mechanical Information

## 4.1 Mechanical Drawing

TOLERANCE UNLESS OTHERWISE SPECIFIED: ±0.1mm

## 5. Packaging Information

**TBD**