# AW-CM389NF

## IEEE 802.11 2X2 MIMO ac/a/b/g/n Wireless LAN + Bluetooth NGFF Module

## **Datasheet**

Version 1.3

| Document<br>release | Date       | Modification                                                                                                                                                                                                                         | Initials   | Approved        |

|---------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|

| Version0.1          | 2013/08/13 | Initial version                                                                                                                                                                                                                      | Kai<br>Wu  | Chihhao<br>Liao |

| Version0.2          | 2013/10/08 | 1. Update Pin Map<br>2. Update Interface Configuration straps                                                                                                                                                                        | Alex Yu    | Chihhao<br>Liao |

| Version0.3          | 2013/11/07 | <ol> <li>Update Pin Map</li> <li>Update Pin Definition</li> <li>Update Dimension</li> </ol>                                                                                                                                          | Alex Yu    | Chihhao<br>Liao |

| Version0.4          | 2013/11/19 | <ol> <li>Update "2 Electrical Characteristic"</li> <li>Update "3-1 SDIO Interface"</li> <li>Update "4 Pin Definition"</li> <li>Update "5 Mechanical Information"</li> <li>Add "2-2.1 The interface pins power<br/>supply"</li> </ol> | Alex Yu    | Chihhao<br>Liao |

| Version0.5          | 2013/12/03 | Add "4 Pin Definition's Notes"                                                                                                                                                                                                       | Alex Yu    | Chihhao<br>Liao |

| Version0.6          | 2013/12/05 | Update "4 Pin Definition's Notes"                                                                                                                                                                                                    | Alex Yu    | Chihhao<br>Liao |

| Version0.7          | 2013/12/11 | 1. Update "1-2 Block Diagram"<br>2. Update "5-2 Module Footprint"                                                                                                                                                                    | Alex Yu    | Chihhao<br>Liao |

| Version0.8          | 2014/03/20 | <ol> <li>Update "1-4 Bluetooth Standard"</li> <li>Update "5-1 Mechanical Information"</li> <li>Update "2-3 Clock Specification"</li> <li>Update "5-2 Module Footprint"</li> <li>Add "7. Shipping Information"</li> </ol>             | Alex Yu    | Chihhao<br>Liao |

| Version0.9          | 2014/04/14 | 1. Update "1-4 Specifications Table"<br>2. Update "5-1 Mechanical Information"                                                                                                                                                       | Alex Yu    | Chihhao<br>Liao |

| Version 1.0         | 2015/01/24 | <ol> <li>Update" Interface supports and<br/>combinations"</li> <li>Update "1-4 Specifications Table"</li> <li>Update "4. Pin Definitions"</li> </ol>                                                                                 | Alex Yu    | Chihhao<br>Liao |

| Version 1.1         | 2015/10/21 | <ol> <li>Update" Interface supports and<br/>combinations</li> <li>Modify operating temperature</li> <li>Support BT4.2</li> </ol>                                                                                                     | Peter Chen | Chihhao<br>Liao |

| Version 1.2         | 2016/11/30 | Remove NFC function                                                                                                                                                                                                                  | Peter Chen | Daniel Lee      |

| Version 1.3         | 2019/08/06 | Correct "5-2 Module Footprint"                                                                                                                                                                                                       | Renton Tao | Daniel Lee      |

#### **1. General Description** 1-1. Product Overview and Functional Description

**AzureWave Technologies, Inc.** introduces the IEEE 802.11ac/a/b/g/n 2X2 MIMO WLAN & Bluetooth NGFF module --- **AW-CM389NF**. The module is targeted to mobile devices including **Notebook, TV, Tablet and Gaming Device** which need small package module, low power consumption, multiple interfaces and OS support. By using AW-CM389NF, the customers can easily enable the Wi-Fi, and BT embedded applications with the benefits of **high design flexibility, short development cycle, and guick time-to-market.**

Compliance with the IEEE 802.11ac/a/b/g/n standard, the AW-CM389NF uses Direct Sequence Spread Spectrum (DSSS), Orthogonal Frequency Division Multiplexing (OFDM), DBPSK, DQPSK, CCK and QAM baseband modulation technologies. A high level of integration and full implementation of the power management functions specified in the IEEE 802.11 standard minimize the system power requirements by using AW-CM389NF. In addition to the support of WPA/WPA2 and WEP 64-bit and 128-bit encryption, the AW-CM389NF also supports the IEEE 802.11i security standard through the implementation of Advanced Encryption Standard (AES)/Counter Mode CBC-MAC Protocol (CCMP), Wired Equivalent Privacy (WEP) with Temporal Key Integrity Protocol (TKIP), Advanced Encryption Standard (AES)/Cipher-Based Message Authentication Code (CMAC), and WLAN Authentication and Privacy Infrastructure (WAPI) security mechanisms.

For the video, voice and multimedia applications the AW-CM389NF support **802.11e Quality of Service** (**QoS**). The device also supports **802.11h Dynamic Frequency Selection (DFS)** for detecting radar pulses when operating in the 5GHz range.

For Bluetooth operation, AW-CM389NF is Bluetooth 4.2 (supports Low Energy).

AW-CM389NF supports **SDIO**, **PCIE**, **USB**, and high speed **UART interfaces** for WLAN and Bluetooth to the host processor.

AW-CM389NF is suitable for multiple mobile processors for different applications with the support **cellular phone co-existence**.

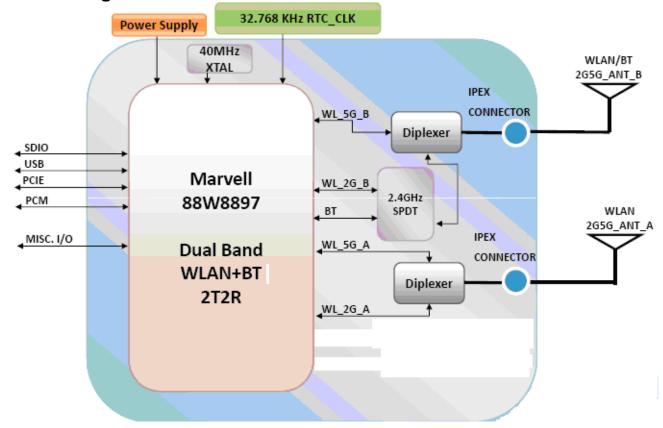

AW-CM389NF module adopts Marvell's latest highly-integrated dual-band WLAN & Bluetooth SoC---88W8897. All the other components are implemented by all means to reach the mechanical specification required.

#### 1-2. Block Diagram

#### Note: Interface supports and combinations as shown below:

| Scenario | WLAN | BT   | BT_AMPS | Firmware<br>Download I/F | Firmware<br>Download Mode | Configuration*  |

|----------|------|------|---------|--------------------------|---------------------------|-----------------|

| 1        | SDIO | SDIO |         | SDIO                     | Serial                    | CON[3:0]=b'0001 |

| 2        | SDIO | SDIO | SDIO    | SDIO                     | Serial                    | CON[3:0]=b'0111 |

| 3        | PCIe | UART |         | PCIe + UART              | Parallel                  | CON[3:0]=b'1111 |

| 4        | PCIe | UART |         | PCIe or UART             | Serial                    | CON[3:0]=b'1100 |

| 5        | PCIe | USB  | USB     | PCle                     | Serial                    | CON[3:0]=b'1110 |

#### \*Configuration pins:

| <u> </u>      |        |                |  |  |  |  |

|---------------|--------|----------------|--|--|--|--|

| Configuration | Pin No | Pin Name       |  |  |  |  |

| CON[3]        | 13     | CONFIG_HOST[3] |  |  |  |  |

| CON[2]        | 10     | CONFIG_HOST[2] |  |  |  |  |

| CON[1]        | 9      | CONFIG_HOST[1] |  |  |  |  |

| CON[0]        | 8      | CONFIG_HOST[0] |  |  |  |  |

#### 1-3. Key feature:

- Small footprint: 12mm(L) x 16mm(W) x 1.4 mm(H)

- SDIO3.0, G-SPI, USB interfaces support for WLAN

- High speed UART, PCM/Inter-IC Sound(I2S) and SDIO3.0, USB for Bluetooth

- Bluetooth 4.2 complaint with Bluetooth 2.1 + Enhanced Data Rate (EDR)

- Audio Codec interface support

- Cellular phone co-existence support

- Multiple power saving modes for low power consumption

- IEEE 802.11i for advanced security

- Quality of Service (QoS) support for multimedia applications

- Drip-in WLAN Linux drivers are Android ready and validated on Android based systems.

- Support for Linux kernel versions up to 2.6.32.

- Support for BlueZ v4.47 Bluetooth profiles stack used in Android Éclair

- Simultaneous AP-STA

- Support China WAPI

- Lead-free design

## 1-4. Specifications Table

| Model Name                | AW-CM389NF                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Description       | 2x2 MIMO Wireless LAN + Bluetooth Combo Module                                                                                                                                                                                                                                                                                                            |

| WLAN Standard             | IEEE 802.11 a/b/g/n/ac, Wi-Fi compliant                                                                                                                                                                                                                                                                                                                   |

| Bluetooth Standard        | Bluetooth 4.2 complaint with Bluetooth 2.1+Enhanced Data Rate (EDR)                                                                                                                                                                                                                                                                                       |

| Host Interface            | USB 2.0 for WLAN and Bluetooth                                                                                                                                                                                                                                                                                                                            |

| Major Chipset             | Marvell 88W8897                                                                                                                                                                                                                                                                                                                                           |

| Dimension                 | 12mm x 16mm x 1.4mm                                                                                                                                                                                                                                                                                                                                       |

| Weight                    | твр                                                                                                                                                                                                                                                                                                                                                       |

| Package                   | LGA                                                                                                                                                                                                                                                                                                                                                       |

| Operating Conditions      |                                                                                                                                                                                                                                                                                                                                                           |

| Voltage                   | 3.3V+- 10%                                                                                                                                                                                                                                                                                                                                                |

| Temperature               | Operating: -30 ~ 85°C ; Storage: -40 ~ 85°C                                                                                                                                                                                                                                                                                                               |

| Electrical Specifications |                                                                                                                                                                                                                                                                                                                                                           |

| Frequency Range           | 2.4 GHz ISM radio band / 5 GHz Unlicensed National Information Infrastructure (U-NII) band                                                                                                                                                                                                                                                                |

| Number of Channels        | 802.11ac: USA-4<br>802.11a: USA, Taiwan – 12/4<br>Most European Countries –19<br>Japan – 4<br>802.11b: USA, Canada and Taiwan – 11<br>Most European Countries – 13<br>France – 4<br>802.11g: USA, Canada and Taiwan – 11<br>Most European Countries – 13<br>Japan – 13<br>802.11n(HT20): Channel 1~13(2412~2472)<br>802.11n(HT40): Channel 1~7(2422~2452) |

| Modulation                | DSSS, OFDM, DBPSK, DQPSK, CCK, 16-QAM, 64-QAM and 256-QAM for<br>WLAN<br>GFSK (1Mbps), Π/4 DQPSK (2Mbps) and 8DPSK (3Mbps) for Bluetooth                                                                                                                                                                                                                  |

| Output Power              | WLAN G band:         11b:16dBm +/- 2dBm(11M)         11g:14dBm +/- 2dBm (54M)         11n:HT20 13dBm +/- 2dBm(MCS7)         WLAN A band:         11a: 13dBm +/- 2dBm(54M)         11n:HT20 12dBm +/- 2dBm(MCS7)         HT40 10dBm +/- 2dBm(MCS7)         HT40 10dBm +/- 2dBm(MCS7)         11ac: 8dBm +/- 2dBm(MCS9)         Bluetooth:         Class 2  |

| Antenna Connector         | Main Connector: WLAN Aux Connector: WLAN + BT                                                                                                                                                                                                                                                                                                             |

| Receive Sensitivity            | WLAN G band :<br>11b:-83dBm (11M)<br>11g:-72dBm (54M)<br>11n:HT20 -68dBm (MCS7)<br>HT40 -65dBm (MCS7)<br>WLAN A band:<br>11a: -67dBm (54M)<br>11n:HT20 -67dBm (MCS7)<br>HT40 -64dBm(MCS7)<br>11ac: -54dBm(MCS9)<br>Bluetooth:<br>DH1:-70dBm<br>3DH5:-70dBm                                                                                             |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Medium Access Protocol         | CSMA/CA with ACK                                                                                                                                                                                                                                                                                                                                       |

| Data Rates                     | WLAN<br>802.11b: 1, 2, 5.5, 11Mbps<br>802.11a/g: 6, 9, 12, 18, 24, 36, 48, 54Mbps<br>802.11n: up to 150Mbps-single<br>802.11n: up to 300Mbps-2x2 MIMO<br>802.11ac:up to 192.6Mbps (20MHz channel)<br>802.11ac:up to 400Mbps (40MHz channel)<br>802.11ac:up to 866.7Mbps (80MHz channel)<br>Bluetooth<br>Bluetooth 2.1+EDR data rates of 1,2, and 3Mbps |

| Power Consumption              | TBD                                                                                                                                                                                                                                                                                                                                                    |

| Operating Range                | Open Space: ~300m ;Indoor: ~100m for WLAN<br>Minimum 10 m indoor for Bluetooth<br>The transmission speed may vary according to the environment)                                                                                                                                                                                                        |

| Security                       | <ul> <li>WAPI</li> <li>WEP 64-bit and 128-bit encryption with H/W TKIP processing</li> <li>WPA/WPA2 (Wi-Fi Protected Access)</li> <li>AES-CCMP hardware implementation as part of 802.11i security standard</li> </ul>                                                                                                                                 |

| Operating System Compatibility | Linux(Android), Windows, More information please contact Azurewave FAE.                                                                                                                                                                                                                                                                                |

| Co-Existence                   | Bluetooth and cell phone(GSM/DCS/WCDMA/UMTS/3G) co-existence                                                                                                                                                                                                                                                                                           |

## 2. Electrical Characteristic 2-1. Absolute Maximum Ratings

| Symbol         | Parameter             | Condition | Min | Тур | Max | Units |

|----------------|-----------------------|-----------|-----|-----|-----|-------|

|                |                       |           |     | 1.8 | 2.2 |       |

| Pin73/ VIO     | Host I/O power supply |           |     | 2.5 | 3.0 | V     |

|                |                       |           |     | 3.3 | 4.0 |       |

| Pin44/ VIO SD  | SDIO power supply     |           |     | 1.8 | 2.2 | V     |

| F11144/ VIO_3D | SDIO power suppry     |           |     | 3.3 | 4.0 | v     |

| Pin5/ 3.3V     | LDO VBAT input        |           |     | 3.3 | 5.0 | V     |

| Pin72/ 3V3_USB | LDO USB VBAT input    |           |     | 3.3 | 4.0 | V     |

| Pin4/ 3.3V     | LDO RF VBAT input     |           |     | 3.3 | 4.0 | V     |

## 2-2. Recommended Operating Conditions

| Symbol         | Parameter              | Condition | Min  | Тур | Max  | Units |

|----------------|------------------------|-----------|------|-----|------|-------|

|                | 1.8V/2.5V/3.3V digital |           | 1.62 | 1.8 | 1.98 |       |

| Pin73/ VIO     | 5                      |           | 2.25 | 2.5 | 2.75 | V     |

|                | I/O power supply       |           | 2.97 | 3.3 | 3.63 |       |

| Pin44/ VIO SD  | 1.8V/3.3V digital I/O  |           | 1.62 | 1.8 | 1.98 | V     |

| FII144/ VIO_3D | SDIO power supply      |           | 2.97 | 3.3 | 3.63 | v     |

| Pin5/ 3.3V     | LDO VBAT input         |           | 2.7  | 3.3 | 5.0  | V     |

| Pin72/ 3V3_USB | LDO USB VBAT input     |           | 2.97 | 3.3 | 3.63 | V     |

| Pin4/ 3.3V     | LDO RF VBAT input      |           | 2.97 | 3.3 | 3.63 | V     |

#### 2-2.1 The interface pins power supply

The SDIO host interface pins are powered from the chip VIO\_SD (pin 44) 1.8V/3.3V voltage supply.

- SDIO Defauld Speed, High Speed Modes (3.3V)

- SDR12, SDR25, SDR50 Modes (up to 100MHz) (1.8V)

- SDR104 Mode (208MHz) (1.8V)

The PCI Express host interface pins are powered from the module's chip LDO 1.8V voltage supply internal. The USB2.0 host interface pins are powered from the 3V3\_USB (pin 72) 3.3V voltage supply.

The UART Tx and Rx pins are powered from the VIO (pin 73) voltage supply.

The GPIO pins are powered from the VIO (pin 73) voltage supply (GPIO [9:8] from 3.3V voltage internal).

The clocked serial pins are powered from the module's chip LDO 1.8V voltage supply internal.

The audio pins are powered from the chip VIO (pin 73) voltage supply.

#### 2-3. Clock Specifications

#### 2-3.1 External Sleep Clock Timing

#### External Sleep Clock is necessary for two reasons:

1. Auto frequency Detection.

This is where the internal logic will bin the Ref clock source to figure out what is the reference clock

frequency is. This is done so no strapping is needed for telling 8897 what the ref clock input is.

2. Allow low current modes for BT to enter sleep modes such as sniff modes.

The AW-CM389NF external sleep clock pin is powered from the 3.3V voltage supply.

| Symbol            | Parameter             | Min                     | Тур          | Мах                 | Units |

|-------------------|-----------------------|-------------------------|--------------|---------------------|-------|

| CLK               | Clock Frequency Range | 32 or 32.768 -<br>50ppm | 32 or 32.768 | 32 or 32.768 +50ppm | KHz   |

| Тнідн             | Clock high time       | 40                      |              |                     | ns    |

| TLOW              | Clock low time        | 40                      |              |                     | ns    |

| T <sub>RISE</sub> | Clock rise time       |                         |              | 5                   | ns    |

| T <sub>FALL</sub> | Clock fall time       |                         |              | 5                   | ns    |

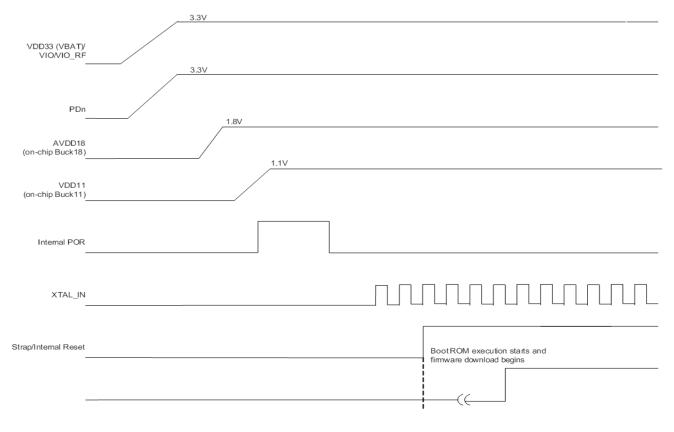

#### 2-4. Reset Configuration

The AW-CM389NF is reset to its default operating state under the following conditions:

- Power-on reset (POR)

- Software/Firmware reset

- External pin reset (RESETn)

#### 2-4-1. Internal Reset

The AW-CM389NF device is reset, and the internal CPU begins the boot sequence when any of the following internal reset events occur:

- Device receives power and VDDL supplies rise (triggers internal POR circuit)

- External pin (PDn) assertion will generate POR

#### 2-4-2. External Reset

The AW-CM389NF is reset when PDn pin is asserted low and the internal CPU begins the boot sequence when the PDn pin transitions from low to high.

## 2-5. Power up Timing Sequence

## 3. Host Interfaces

## 3-1. SDIO Interface

The AW-CM389NF supports a SDIO device interface that conforms to the industry standard SDIO Full-Speed card specification and allows a host controller using the SDIO bus protocol to access the Wireless module device.

The AW-CM389NF acts as the device on the SDIO bus. The host unit can access registers of the SDIO interface directly and can access shared memory in the device through the use of BARs and a DMA engine.

The SDIO device interface main features include:

Supports SDIO 3.0 Standard

On-chip memory used for CIS

Supports SPI, 1-bit SDIO, and 4-bit SDIO transfer modes

Special interrupt register for information exchange

Allows card to interrupt host

## 3-1-1. SDIO Interface Signal Description

|           | Signal | Туре |                                                            |

|-----------|--------|------|------------------------------------------------------------|

| Pin Name  | Name   |      | Description                                                |

| SD_CLK    | CLK    | I/O  | SDIO 1-bit mode: Clock                                     |

|           |        |      | SDIO SPI mode: Clock                                       |

| SD_CMD    | CMD    | I/O  | SDIO 1-bit mode: Command line                              |

|           |        |      | SDIO SPI mode: Data input                                  |

| SD_DAT[3] | DAT3   | I/O  | SDIO 4-bit mode: Data line bit [3]                         |

|           |        |      | SDIO 1-bit mode: Not used                                  |

|           |        |      | SDIO SPI mode: Chip select (active low)                    |

| SD_DAT[2] | DAT2   | I/O  | SDIO 4-bit mode: Data line bit [2] or Read Wait (optional) |

|           |        |      | SDIO 1-bit mode: Read Wait (optional)                      |

|           |        |      | SDIO SPII mode: Reserved                                   |

| SD_DAT[1] | DAT1   | I/O  | SDIO 4-bit mode: Data line bit [1]                         |

|           |        |      | SDIO 1-bit mode: Interrupt                                 |

|           |        |      | SDIO SPI mode: Interrupt                                   |

| SD_DAT[0] | DAT0   | I/O  | SDIO 4-bit mode: Data line bit [0]                         |

|           |        |      | SDIO 1-bit mode: Data line                                 |

|           |        |      | SDIO SPI mode: Data output                                 |

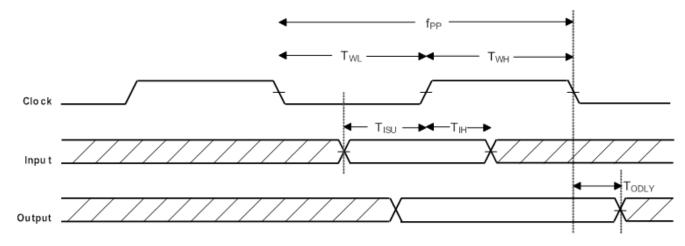

#### 3-1-2. Default Speed, High Speed Modes (3.3V)

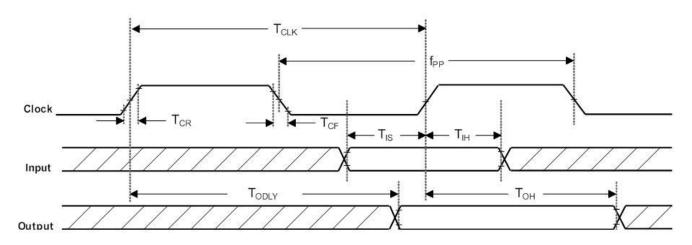

SDIO Protocol Timing Diagram – Default Speed Mode (3.3V)

#### SDIO Protocol Timing Diagram – HighSpeed Mode (3.3V)

#### Table shows SDIO Timing Data—Default Speed, High Speed Modes (3.3V)

NOTE: Over full range of values specified in the Recommended Operating Conditions unless otherwise specified.

| Sy mbol           | Par ameter          | Con dit io n  | Min | Тур | Max | Units |

|-------------------|---------------------|---------------|-----|-----|-----|-------|

| f <sub>PP</sub>   | Clock Frequency     | Default Speed | 0   |     | 25  | MHz   |

|                   |                     | High Speed    | 0   |     | 50  | MHz   |

| T <sub>WL</sub>   | Clock Low Time      | Default Speed | 10  |     |     | ns    |

|                   |                     | High Speed    | 7   |     |     | ns    |

| т <sub>wн</sub>   | Clock High Time     | Default Speed | 10  |     |     | ns    |

|                   |                     | High Speed    | 7   |     |     | ns    |

| T <sub>ISU</sub>  | Input Setup Time    | Default Speed | 5   |     |     | ns    |

|                   |                     | High Speed    | 6   |     |     | ns    |

| т <sub>IH</sub>   | Input Hold Time     | Default Speed | 5   |     |     | ns    |

|                   |                     | High Speed    | 2   |     |     | ns    |

| T <sub>ODLY</sub> | Output Delay Time   | Default Speed |     |     | 14  | ns    |

|                   | CL ≤ 40 pF (1 card) | High Speed    |     | -1  | 4   | ns    |

| тон               | Output Hold Time    | High Speed    | 2.5 |     |     | ns    |

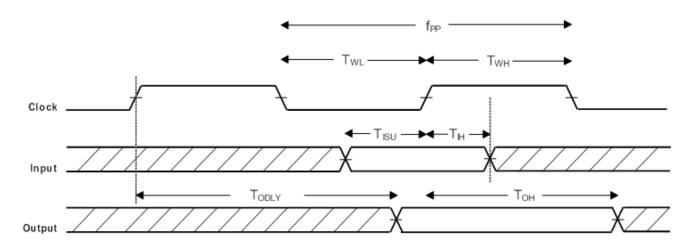

## 3-1-3. SDR12, SDR25, SDR50 Modes (up to 100MHz) (1.8V)

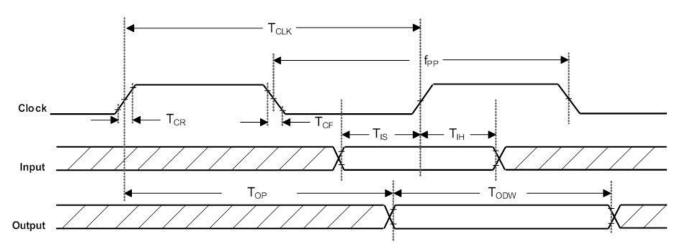

SDIO Protocol Timing Diagram – SDR12, SDR25, SDR50 Modes (up to 100MHz) (1.8V)

#### Table shows SDIO Timing Data—SDR12,SDR25,SDR50 Modes (up to 100MHz) (1.8V)

| Symbol                            | Parameter                                                                                                      | Condit ion  | Min | Тур   | Max                  | Units |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-------------|-----|-------|----------------------|-------|

| f <sub>PP</sub>                   | Clock frequency                                                                                                | SDR12/25/50 | 25  | 576   | 100                  | MHz   |

| T <sub>IS</sub>                   | Input setup time                                                                                               | SDR12/25/50 | 3   | 1773  |                      | ns    |

| тн                                | Input hold time                                                                                                | SDR12/25/50 | 0.8 | -     | 3 <del></del> ()     | ns    |

| T <sub>CLK</sub>                  | Clock time                                                                                                     | SDR12/25/50 | 10  | 0.00  | 40                   | ns    |

| T <sub>CR</sub> , T <sub>CF</sub> | Rise time, fall time<br>T <sub>CR</sub> , T <sub>CF</sub> < 2 ns (max) at 100 MHz<br>C <sub>CARD</sub> = 10 pF | SDR12/25/50 |     |       | 0.2*T <sub>CLK</sub> | ns    |

| T <sub>ODLY</sub>                 | Output delay time $C_L \leq 30 \text{ pF}$                                                                     | SDR12/25/50 |     | 60000 | 7.5                  | ns    |

| т <sub>он</sub>                   | Output hold time<br>C <sub>L</sub> = 15 pF                                                                     | SDR12/25/50 | 1.5 | H     |                      | ns    |

#### 3-1-4. SDR104 Modes (208MHz) (1.8V)

#### SDIO Protocol Timing Diagram –SDR104 Mode (208MHz)

#### Table shows SDIO Timing Data—SDR104 Mode (208MHz)

| Sy m bol                          | Parameter                                                                                                         | Condit ion | Min  | Тур  | Max                  | Units |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|------------|------|------|----------------------|-------|

| f <sub>PP</sub>                   | Clock frequency                                                                                                   | SDR104     | 0    | 144  | 208                  | MHz   |

| T <sub>IS</sub>                   | Input setup time                                                                                                  | SDR104     | 1.4  |      |                      | ns    |

| т <sub>н</sub>                    | Input hold time                                                                                                   | SDR104     | 0.8  |      |                      | ns    |

| T <sub>CLK</sub>                  | Clock time                                                                                                        | SDR104     | 4.8  |      |                      | ns    |

| T <sub>CR</sub> , T <sub>CF</sub> | Rise time, fall time<br>T <sub>CR</sub> , T <sub>CF</sub> < 0.96 ns (max) at 208 MHz<br>C <sub>CARD</sub> = 10 pF | SDR104     |      |      | 0.2*T <sub>CLK</sub> | ns    |

| Т <sub>ОР</sub>                   | Card output phase                                                                                                 | SDR104     | 0    | -    | 10                   | ns    |

| T <sub>ODW</sub>                  | Output timing of variable data window                                                                             | SDR104     | 2.88 | 1220 | 220                  | ns    |

#### **3-2. PCI Express Interface**

## **3-2-1 Differential Tx Output Electricals**

| Symbol                                         | Paramete r                                                                                            | Min    | Тур  | Max    | Unit s |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|------|--------|--------|

| UI                                             | Unit interval<br>Each UI is 400 ps ±300 PPM.<br>UI does not account for SSC dictated variations.      | 399.98 | 400  | 400.12 | ps     |

| V <sub>Tx_DIFFpp</sub>                         | Differential peak-to-peak output voltage<br>$V_{Tx_DIFFpp} = 2^{*} V_{TX-D+} - V_{TX-D} $             | 0.800  |      | 1.2    | V      |

| VTx_DE_RATIO                                   | De-emphasized differential output voltage (ratio)                                                     | -3.0   | -3.5 | -4.0   | db     |

| T <sub>RX_EYE</sub>                            | Minimum Tx eye wid th                                                                                 | 0.75   |      |        | UI     |

| T <sub>RX_EYE_MEDIAN</sub> _<br>MAX_JIT        | Maximum time between jitter median and maximum deviation from median                                  |        |      | 0.125  | UI     |

| T <sub>Tx_RISE</sub> ,<br>T <sub>Tx_FALL</sub> | D+/D- Tx output rise/fall time                                                                        | 0.125  |      |        | UI     |

| VTX_CM_DC_ACTIV<br>E_IDLE_DELTA                | Absolute delta of DC common mode voltage during L0 and electrical idle                                | 0-     | -    | 100    | mV     |

| V <sub>Tx_CM_DC_LINE_</sub><br>DE LTA          | Absolute delta of DC common mode voltage between D+ and D-                                            | 0-     | -    | 25     | mV     |

| VTx_IDLE_D IFF p                               | Electrical idle differential peak output voltage                                                      | 0      |      | 20     | mV     |

| VTX_RCV_DETECT                                 | Voltage change allowed during receiver detection                                                      |        |      | 600    | mV     |

| V <sub>Tx_DC_CM</sub>                          | TxDC common mode voltage                                                                              |        |      | 3.6    | V      |

| ITX_SHORT                                      | Tx short circuit current limit                                                                        |        |      | 90     | mA     |

| T <sub>TX_IDLE_MIN</sub>                       | Minimum time spent in electrical idle                                                                 | 50     |      |        | UI     |

| T <sub>TX_IDLE_SET_TO_</sub>                   | Maximum time to transition to a valid electrical idle after<br>sending an electrical idle ordered set |        |      | 20     | UI     |

| T <sub>TX_IDLE_TO_DIFF_</sub>                  | Maximum time to transition to valid Tx specifications after leaving an electrical idle condition      |        |      | 20     | UI     |

| RL <sub>Tx_DIFF</sub>                          | Differential return loss                                                                              | 10     |      |        | dB     |

| RL <sub>Tx_CM</sub>                            | Common mode return loss                                                                               | 6      |      |        | dB     |

| C <sub>Tx</sub>                                | AC coupling capacitor                                                                                 | 75     |      | 200    | nF     |

| T <sub>Crosstalk</sub>                         | Crosstalk random timeout                                                                              | 0      |      | 1      | ms     |

## 3-2-2 Differential Rx Output Electricals

| Sy m bol                                    | Paramet er                                                                                       | Min    | Тур | Max    | Unit s |

|---------------------------------------------|--------------------------------------------------------------------------------------------------|--------|-----|--------|--------|

| UI                                          | Unit interval<br>Each UI is 400 ps ±300 ppm.<br>UI does not account for SSC dictated variations. | 399.98 | 400 | 400.12 | ps     |

| $V_{Rx\_DIFFpp}$                            | Differential peak-to-peak voltage<br>$V_{Rx\_DIFFpp} = 2^* V_{RX-D+} - V_{RX-D-} $               | 0.175  |     | 1.2    | V      |

| T <sub>Rx_EYE</sub>                         | Minimum receiver eye width                                                                       | 0.4    |     |        | UI     |

| T <sub>Rx_EYE_MEDIAN_MAX_</sub><br>JIT      | Maximum time between jitter median and maximum deviation from median                             |        |     | 0.3    | UI     |

| V <sub>Rx_CM_ACp</sub>                      | AC peak common mode input voltage                                                                |        |     | 150    | mV     |

| RL <sub>Rx_DIFF</sub>                       | Differential return loss                                                                         | 10     |     |        | dB     |

| RL <sub>Rx_CM</sub>                         | Common mode return loss                                                                          | 6      |     |        | dB     |

| Z <sub>Rx_DIFF_DC</sub>                     | DC differential input impedance                                                                  | 80     | 100 | 120    | Ω      |

| Z <sub>Rx_DC</sub>                          | DC input impedance                                                                               | 40     | 50  | 60     | Ω      |

| Z <sub>Rx_HIGH_IMP_DC_POS</sub>             | Powered down DC input impedance positive                                                         | 50     |     |        | k      |

| Z <sub>Rx_HIGH_IMP_DC_NEG</sub>             | Powered down DC input impedance negative                                                         | 1      |     |        | kΩ     |

| V <sub>Rx_IDLE_DET_</sub><br>DIFFpp         | Electrical idle detect threshold                                                                 | 65     |     | 175    | mV     |

| T <sub>Rx_IDLE_DET_</sub><br>DIFF_ENTERTIME | Unexpected electrical idle enter detect threshold integration time                               |        |     | 10     | ms     |

| L <sub>Rx_SKEW</sub>                        | Total skew                                                                                       |        | -2  | 0      | ns     |

### 3-3. USB Interface

The USB device interface is compliant with the Universal Serial Bus Specification, Revision 2.0, April 27, 2000. A USB host uses the USB cable bus and the USB 2.0 device interface to communicate with the chip.

The main features of the USB device interface include:

High/full speed operation (480/12 Mbps)

Suspend/host resume/device resume (remote wake-up)

Built-in DMA engine that reduces interrupt loads on the embedded processor and reduces the system bus bandwidth requirement for serving the USB device operation

The USB 2.0 device interface is designed with 3.3V signal level pads.

#### 3-3-1. USB 2.0 Device Interface Description

Table shows the signal mapping between the AW-CM389NF and the USB Specification, Revision 2.0.

| Pin Name          | USB 2.0<br>Specification<br>Pin Name | Description                                                                                                        |

|-------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Pin72/<br>3V3_USB | VBUS                                 | USB Bus Power Supply<br>On-board regulator regulates voltage from VBUS level to<br>voltage levels used by USB PHY. |

|                   | GND                                  | USB Bus Ground<br>Common ground on SoC device.                                                                     |

| Pin70/<br>USB_DP  | D+                                   | USB Bus Data Positive.<br>One of the differential data pair.                                                       |

| Pin69/<br>USB_DN  | D-                                   | USB Bus Data Negative.<br>One of the differential data pair.                                                       |

#### 3-3-2. USB 2.0 Device Functional Description

The device controller uses internal Scatter/Gather DMA engine to transfer the transmit packet from internal SRAM to USB and the receive packet from USB to internal SRAM. The Device IN Endpoint DMA (DIEPDMAn) and Device OUT Endpoint DMA (DOEPDMAn) registers are used by the DMA engine to access the base descriptor. The application is interrupted after the programmed transfer size extracted from the descriptors is transmitted or received. By using registers, interrupts, and special data structures, the device controller can communicate with the device controller driver (application/software) about bus states, host request, and data transfer status. The device controller driver also has all of the routines to respond to the device framework commands issued by a USB host, so it controls the attachment, configuration, operation, and detachment of the device.

### 3-4. High-Speed UART Interface

The AW-CM389NF supports a high-speed Universal Asynchronous Receiver/Transmitter (UART) interface, compliant to the industry standard 16550 specification. High-speed baud rates are supported to provide the physical transport between the device and the host for exchanging Bluetooth data. Table shows the rates supported.

The UART interface features include:

- FIFO mode permanently selected for transmit and receive operations

- Two pins for transmit and receive operations

Two flow control pins

Interrupt triggers for low-power, high throughput operation

The UART interface operation includes:

Upload boot code to the internal CPU (for debug purposes)

Support diagnostic tests

Support data input/output operations for peripheral devices connected through a standard UART interface

#### UART Baud Rates Supported

| Baud Rate |        |         |         |         |  |

|-----------|--------|---------|---------|---------|--|

| 1200      | 38400  | 460800  | 1500000 | 3000000 |  |

| 2400      | 57600  | 500000  | 1843200 | 3250000 |  |

| 4800      | 76800  | 921600  | 2000000 | 3692300 |  |

| 9600      | 115200 | 1000000 | 2100000 | 4000000 |  |

| 19200     | 230400 | 1382400 | 2764800 |         |  |

## 3-4-1. UART Interface Signal Description

Table shows the standard UART signal names on the device.

| Signal Name   | 16550<br>Standard<br>Pin Name | Description                                                                  |

|---------------|-------------------------------|------------------------------------------------------------------------------|

| Data Bus      |                               |                                                                              |

| UART_SIN      | SIN                           | Serial data input from modem, data set, or peripheral device                 |

| UART_SOUT     | SOUT                          | Serial data output from modem, data set, or peripheral device                |

| Modem Control |                               |                                                                              |

| UART_RTSN     | RTS                           | Request To Send output to modem, data set, or peripheral device (active low) |

| UART_CTSN     | CTS                           | Clear To Send input from modem, data set, or peripheral device (active low)  |

|               |                               |                                                                              |

#### 3-4-2. UART Interface Functional Description

#### 3-3-2-1. Booting from UART

When booting from the UART, the AW-CM389NF device has the following requirements:

| System Requirement  | Description |

|---------------------|-------------|

| Number of data bits | 8 bits      |

| Stop bits           | 1 bit       |

| Parity              | No parity   |

| Baud Rate           | 115200      |

#### 3-4-2-2. UART as Test Port

Test diagnostic programs may be uploaded to the CPU through the UART interface. During execution, the diagnostic program transmits performance and status information through the UART by performing a write to the PBU address space designated to the UART.

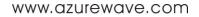

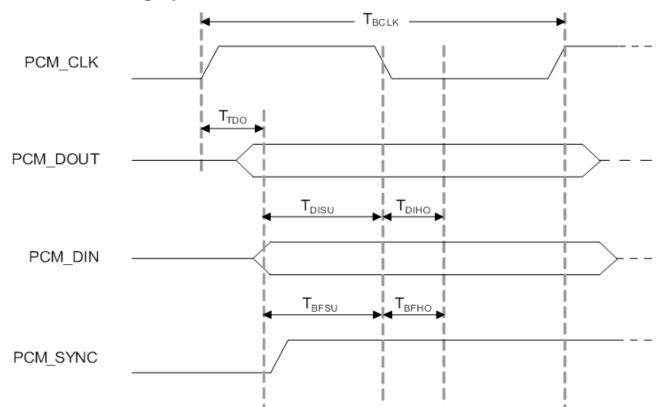

#### 3-5. PCM Interface

#### 3-5-1. PCM Timing Specification – Master Mode

| Sy mbol                    | Parameter | Con diti on | Min | Тур     | Max | Unit s |

|----------------------------|-----------|-------------|-----|---------|-----|--------|

| FBCLK                      |           |             |     | 2/2.048 |     | MHz    |

| Duty Cycle <sub>BCLK</sub> |           |             | 0.4 | 0.5     | 0.6 |        |

| TBCLK rise/fall            |           |             |     | 3       |     | ns     |

| T <sub>DO</sub>            |           |             |     |         | 15  | ns     |

| T <sub>DIS U</sub>         |           |             | 20  |         |     | ns     |

| T <sub>DH O</sub>          |           |             | 15  |         |     | ns     |

| T <sub>BF</sub>            |           |             |     |         | 15  | ns     |

#### 3-5-2. PCM Timing Specification – Slave Mode

| Symbol                      | Parameter | Condition | Min | Тур     | Max | Unit s |

|-----------------------------|-----------|-----------|-----|---------|-----|--------|

| F <sub>BCLK</sub>           |           |           |     | 2/2.048 |     | MHz    |

| Duty Cycle <sub>BCLK</sub>  |           |           | 0.4 | 0.5     | 0.6 |        |

| T <sub>BCLK</sub> rise/fall |           |           |     | 3       |     | ns     |

| T <sub>DO</sub>             |           |           |     |         | 30  | ns     |

| T <sub>DISU</sub>           |           |           | 15  |         |     | ns     |

| т <sub>ыно</sub>            |           |           | 10  |         |     | ns     |

| T <sub>BFSU</sub>           |           |           | 15  |         |     | ns     |

| T <sub>BFHO</sub>           |           |           | 10  |         |     | ns     |

## 4. Pin Definition

|        | Definition       |                                                                                                                                                                                                           |      |

|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Pin No | Definition       | Basic Description                                                                                                                                                                                         | Туре |

| 1      | TMS              | JTAG controller select                                                                                                                                                                                    |      |

| 2      | TCK              | JTAG test clock                                                                                                                                                                                           |      |

| 3      | TDI              | JTAG test data(input)                                                                                                                                                                                     | I    |

| 4      | 3.3V             | 3.3V Analog RF Power Supply                                                                                                                                                                               | I    |

| 5      | 3.3V             | 3.3V VBAT system power supply input                                                                                                                                                                       | I    |

| 6      | GND              | System Ground Pin                                                                                                                                                                                         |      |

| 7      | TDO              | JTAG test data(output)                                                                                                                                                                                    | 0    |

| 8      | CONFIG_HOST[0]   | Configuration: CONFIG_HOST[0]                                                                                                                                                                             |      |

| 9      | CONFIG_HOST[1]   | Configuration: CONFIG_HOST[1]                                                                                                                                                                             |      |

| 10     | CONFIG_HOST[2]   | Configuration: CONFIG_HOST[2]                                                                                                                                                                             |      |

| 11     | GPIO[1]/LTE_SOUT | UART_LTE_SOUT (output)                                                                                                                                                                                    | I    |

| 12     | GPIO[2]/LTE_SIN  | UART_LTE_SIN (input)                                                                                                                                                                                      | I    |

| 13     | CONFIG_HOST[3]   | Configuration: CONFIG_HOST[3]                                                                                                                                                                             |      |

| 14     | GPIO[10]         | GPIO[10] (input/output)                                                                                                                                                                                   |      |

| 15     | NC               | No Connect                                                                                                                                                                                                |      |

| 16     | NC               | No Connect                                                                                                                                                                                                |      |

| 17     | GND              | System Ground Pin                                                                                                                                                                                         |      |

| 18     | NC               | No Connect                                                                                                                                                                                                |      |

| 19     | NC               | No Connect                                                                                                                                                                                                |      |

| 20     | GND              | System Ground Pin                                                                                                                                                                                         |      |

| 21     | NC               | No Connect                                                                                                                                                                                                |      |

| 22     | NC               | No Connect                                                                                                                                                                                                |      |

| 23     | GND              | System Ground Pin                                                                                                                                                                                         |      |

| 24     | NC               | No Connect                                                                                                                                                                                                |      |

| 25     | NC               | No Connect                                                                                                                                                                                                |      |

| 26     | GND              | System Ground Pin                                                                                                                                                                                         |      |

| 27     | SLP_CLK          | Sleep Clock Input<br>Used for WLAN and Bluetooth low-<br>power modes. External sleep clock of 32.768 KHz must be used for auto<br>reference clock calibration and for WLAN/Bluetooth low power operation. | I    |

| Pin No | Definition           | Basic Description                                             | Туре |

|--------|----------------------|---------------------------------------------------------------|------|

| 28     | GPIO[13]/BT IRQ(O)   | GPIO[13] (input/output)                                       | I/O  |

| 29     | PCIE_WAKEn           | PCIe wake signal (output) (active low)                        | 0    |

| 30     | PCIE_CLKREQn         | PCIe clock request (input/output) (active low)                | I/O  |

| 31     | GPIO[12]/PCIE_PERSTn | PCIe host indication to reset the device (input) (active low) | I    |

| 32     | GND                  | System Ground Pin                                             |      |

| 33     | PCIE_RCLK_N          | PCI Express Differential Clock Input—Negative                 | I.   |

| 34     | PCIE_RCLK_P          | PCI Express Differential Clock Input—Positive                 | I.   |

| 35     | GND                  | System Ground Pin                                             |      |

| 36     | PCIE_TX_N            | PCI Express Transmit Data—Negative                            | ο    |

| 37     | PCIE_TX_P            | PCI Express Transmit Data—Positive                            | 0    |

| 38     | GND                  | System Ground Pin                                             |      |

| 39     | PCIE_RX_N            | PCI Express Receive Data—Negative                             | I    |

| 40     | PCIE_RX_P            | PCI Express Receive Data—Positive                             | I    |

| 41     | GND                  | System Ground Pin                                             |      |

| 42     | GPIO[0]/CLK_REQ      | GPIO[0] (input/output)                                        | 0    |

| 43     | GPIO[11]             | GPIO[11] (input/output)                                       |      |

| 44     | VIO_SD               | 1.8V/3.3V Digital I/O SDIO Power Supply                       | I    |

| 45     | PDn                  | Full Power Down (input) (active low)                          | I    |

| 46     | GPIO[3]/WLAN IRQ(O)  | GPIO[3] (input/output)                                        | I    |

| 47     | SD_DAT[3]            | SDIO Data line Bit[3]                                         | I/O  |

| 48     | SD_DAT[2]            | SDIO Data line Bit[2]                                         | I/O  |

| 49     | SD_DAT[1]            | SDIO Data line Bit[1]                                         | I/O  |

| 50     | SD_DAT[0]            | SDIO Data line Bit[0]                                         | I/O  |

| 51     | SD_CMD               | SDIO Command/response (input/output)                          | I/O  |

| 52     | SD_CLK               | SDIO Clock input                                              | I    |

| 53     | NC                   | No Connect                                                    |      |

| 54     | GPIO[6]              | UART_CTSn (input)                                             | I    |

| 55     | GPIO[4]              | UART_SOUT (output)                                            | 0    |

| 56     | GPIO[5]              | UART_SIN (input)                                              | I    |

| 57     | GPIO[7]              | UART_RTSn (output)                                            | 0    |

| 58     | GPIO[22]/PCM_SYNC    | GPIO[22] (input/output)                                       | I/O  |

| Pin No | Definition       | Basic Description                     | Туре |

|--------|------------------|---------------------------------------|------|

| 59     | GPIO[19]/PCM_IN  | GPIO[19] (input/output)               | I    |

| 60     | GPIO[20]/PCM_OUT | GPIO[20] (input/output)               | 0    |

| 61     | GPIO[21]/PCM_CLK | GPIO[21] (input/output)               | I/O  |

| 62     | GND              | System Ground Pin                     |      |

| 63     | GPIO[14]         | GPIO[14] (input/output)               | I/O  |

| 64     | GPIO[8]/WLAN_LED | LED_OUT_WLAN (output)                 | 0    |

| 65     | GPIO[9]/BT_LED   | LED_OUT_BT (output)                   | 0    |

| 66     | NC               | No Connect                            |      |

| 67     | NC               | No Connect                            |      |

| 68     | GND              | System Ground Pin                     |      |

| 69     | USB_DN           | USB Serial Differential Data Negative | I/O  |

| 70     | USB_DP           | USB Serial Differential Data Positive | I/O  |

| 71     | GND              | System Ground Pin                     |      |

| 72     | 3V3_USB          | 3.3V USB Power Supply                 | I    |

| 73     | VIO              | Digital I/O Power Supply              | I    |

| 74     | GND              | System Ground Pin                     |      |

| 75     | GND              | System Ground Pin                     |      |

| 76     | GND              | System Ground Pin                     |      |

| 77     | GND              | System Ground Pin                     |      |

| 78     | GND              | System Ground Pin                     |      |

| 79     | GND              | System Ground Pin                     |      |

| 80     | GND              | System Ground Pin                     |      |

| 81     | GND              | System Ground Pin                     |      |

| 82     | GND              | System Ground Pin                     |      |

| 83     | GND              | System Ground Pin                     |      |

| 84     | GND              | System Ground Pin                     |      |

| 85     | GND              | System Ground Pin                     |      |

| 86     | GND              | System Ground Pin                     |      |

| 87     | GND              | System Ground Pin                     |      |

| 88     | GND              | System Ground Pin                     |      |

| 89     | GND              | System Ground Pin                     |      |

| Pin No | Definition | Basic Description | Туре |

|--------|------------|-------------------|------|

| 90     | GND        | System Ground Pin |      |

| 91     | GND        | System Ground Pin |      |

| 92     | GND        | System Ground Pin |      |

| 93     | GND        | System Ground Pin |      |

| 94     | GND        | System Ground Pin |      |

| 95     | GND        | System Ground Pin |      |

| 96     | GND        | System Ground Pin |      |

| G1     | GND        | System Ground Pin |      |

| G2     | GND        | System Ground Pin |      |

| G3     | GND        | System Ground Pin |      |

| G4     | GND        | System Ground Pin |      |

| G5     | GND        | System Ground Pin |      |

| G6     | GND        | System Ground Pin |      |

| G7     | GND        | System Ground Pin |      |

| G8     | GND        | System Ground Pin |      |

| G9     | GND        | System Ground Pin |      |

| G10    | GND        | System Ground Pin |      |

| G11    | GND        | System Ground Pin |      |

| G12    | GND        | System Ground Pin |      |

| G13    | GND        | System Ground Pin |      |

| G14    | GND        | System Ground Pin |      |

| G15    | GND        | System Ground Pin |      |

| G16    | GND        | System Ground Pin |      |

| G17    | GND        | System Ground Pin |      |

| G18    | GND        | System Ground Pin |      |

| G19    | GND        | System Ground Pin |      |

| G20    | GND        | System Ground Pin |      |

| G21    | GND        | System Ground Pin |      |

| G22    | GND        | System Ground Pin |      |

| G23    | GND        | System Ground Pin |      |

| G24    | GND        | System Ground Pin |      |

| Pin No | Definition | Basic Description | Туре |

|--------|------------|-------------------|------|

| G25    | GND        | System Ground Pin |      |

| G26    | GND        | System Ground Pin |      |

| G27    | GND        | System Ground Pin |      |

| G28    | GND        | System Ground Pin |      |

| G29    | GND        | System Ground Pin |      |

| G30    | GND        | System Ground Pin |      |

| G31    | GND        | System Ground Pin |      |

| G32    | GND        | System Ground Pin |      |

| G33    | GND        | System Ground Pin |      |

| G34    | GND        | System Ground Pin |      |

| G35    | GND        | System Ground Pin |      |

| G36    | GND        | System Ground Pin |      |

#### Notes:

- 1. SDIO signals should have 50 ohm impedances.

- 2. For SDIO interface, 33ohm inline resistor may be needed to help with signal integrity.

- 3. For GPIO[8] ,it's internal pull up to VIO-RF(3.3V).

- 4. For GPIO[9] ,it's internal pull up to VIO-RF(3.3V).

- 5. For PDn pin ,please pull up resistor(51k ohm) to host or VBAT(3V3).

- 6. For SDIO interface, the pull up value is between 10K to 100K ohm according to the SDIO v3.0 SPEC.

- 7. PCIE Impedance targets: Single-ended Z of 60 ohms +- 15%. Differential Impedance of ~100 ohm +- 20%.

- 8. USB Impedance targets: D+/D- are differential and should have 90ohms impedance.

- 9. For GPIO[3] pin ,please pull up resistor(10k ohm) to VIO.

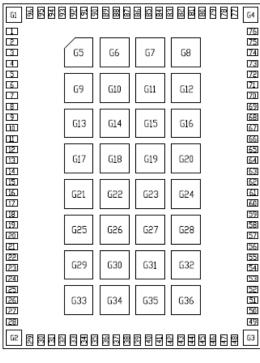

## 4-1 Pin Map

|    |                     |            |              |                | A       | W       | -C          | M:    | 589       | Nŀ        | T       | op      | Vi       | ew    | Pi                 | n ľ      | Vla     | р       |                       |                   |           |                  |                   |    |

|----|---------------------|------------|--------------|----------------|---------|---------|-------------|-------|-----------|-----------|---------|---------|----------|-------|--------------------|----------|---------|---------|-----------------------|-------------------|-----------|------------------|-------------------|----|

|    |                     | 96         | 95           | 94             | 93      | 92      | 91          | 90    | 89        | 88        | 87      | 86      | 85       | 84    | 83                 | 82       | 81      | 80      | 79                    | 78                | Π         |                  |                   | _  |

|    | gnd(g1)             | GND        | GND          | GND            | GND     | GND     | (CND)       | GND   | GND       | GND       | GND     | GND     | GND      | GND   | GND                | GND      | GND     | GND     | GND                   | GND               | GND       |                  | GND(G4)           |    |

| 11 | TMS                 |            |              |                |         |         |             | _     |           |           |         |         |          |       |                    |          |         |         |                       |                   |           | Т                | GND               | 76 |

| 2  | TCK                 |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           |                  | GND               | 75 |

| 3  | TDI                 |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           | GND              | 74                |    |

| 4  | 3.3VRF              | G5 GND     |              |                | G13 GND |         |             |       |           | [         | G21 GND |         |          |       |                    |          | G       | 29 GI   | ١D)                   |                   | VIO       | 73               |                   |    |

| 5  | 3.3VBAT             |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   | 3.3VUSB   | 72               |                   |    |

| 6  | GND                 |            |              |                |         |         |             |       |           |           | •       |         |          |       |                    |          |         |         |                       |                   | •         |                  | GND               | 71 |

| 7  | TDO                 | G6 GND     |              |                |         | G14 GND |             |       |           |           |         | G22 GND |          |       |                    |          |         | G30 GND |                       |                   |           |                  | USB_D+            | 70 |

| 8  | CONFIG_HOST[0]      |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   | USB_D-    | 69               |                   |    |

| 9  | CONFIG_HOST[1]      |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           | GND              | 68                |    |

| 10 | CONFIG_HOST[2]      | G7 GND     |              |                |         |         | G           | 15 GN | ID:       |           | G23 GND |         |          |       |                    |          | G31 GND |         |                       |                   |           | NC               | 67*               |    |

| 11 | GPIO[1] LTE_SOUT(0) |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           |                  | NC                | 66 |

| 12 | GPI0[2]LTE_SIN(I)   |            |              |                |         |         |             |       |           |           |         |         | _        |       |                    | _        |         |         |                       |                   | _         |                  | GPIO[9]LED_BT     | 65 |

| 13 | CONFIG_HOST[3]      |            | 3            | 38. GN         | D)      |         |             | G     | 16 GN     | ID.       |         |         | G        | 24 GN | ID.                |          |         | G       | 32 GI                 | ND.               |           |                  | GPIO(8)LED_WLAN   | 64 |

| 14 | GPI0[10]            |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           |                  | GPIO[14]          | 63 |

| 15 | NC                  |            |              |                |         |         |             |       |           |           | L       |         |          |       |                    |          |         |         |                       |                   | ļ         |                  | GND               | 62 |

| 16 | NC                  |            | Ċ            | 39 GN          | D       | 1       |             | G     | 17 GN     | ND:       | I       |         | G        | 25 GM | ۱D)                | 1        |         | G       | 33 GN                 | ND.               | I         |                  | GPIO[21]/PCM_CLK  | 61 |

| 17 | GND                 | SUS CITINS |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           | GPI0[20]/PCM_OUT | 60                |    |

| 18 | NC                  |            |              |                |         |         |             |       |           |           | L       |         |          |       |                    |          |         |         |                       |                   |           |                  | GPIO[19]/PCM_IN   | 59 |

| 19 | NC                  | G10 GND    |              | G18 GND        |         |         |             |       |           | G26 GND   |         |         |          |       |                    | G        | 34 GN   | ND.     |                       | GPIO[22]/PCM_SYNC | -         |                  |                   |    |

| 20 | GND                 |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       | GPIO[7]/UART RTSn | 57        |                  |                   |    |

| 21 | NC                  |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       | GPIO(5)/UART SIN  | 56        |                  |                   |    |

| 22 | NC                  | G11 GND    |              |                |         | G       | 19 GN       | ID:   | [         | G27 GND   |         |         |          |       |                    | G        | 35 GN   | ND.     |                       | GPIO[4]/UART SOUT | 55        |                  |                   |    |

| 23 | GND                 |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           |                  | GPIO[6]/UART CTSn | 54 |

| 24 | NC                  |            |              |                |         | •       |             |       |           |           | •       |         |          |       |                    | •        |         |         |                       |                   | •         |                  | NC                | 53 |

| 25 | NC                  |            | G            | 12 GI          | ND.     |         |             | G     | 20 GN     | ID:       | [       |         | G        | 28 GM | Ð                  |          |         | G       | 36 GN                 | ۱D.               | Ī         |                  | SDIO CLK          | 52 |

| 26 | GND                 |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           |                  | SDIO CMD          | 51 |

| 27 | SLPCLK              |            |              |                |         |         |             |       |           |           | •       |         |          |       |                    |          |         |         |                       |                   | •         |                  | SDIO DAT0         | 50 |

| 28 | GPI0[13]/BT IRQ(O)  |            |              |                |         |         |             |       |           |           |         |         |          |       |                    |          |         |         |                       |                   |           |                  | SDIO DAT1         | 49 |

|    | GND(G2)             | PCIE_WAKEn | PCIE_CLKREQN | GPIO[12]POIE_F | GND     |         | POIE_ROLK_P | GND   | POIE_TX_N | PCIE_TX_P | GND     |         | POIERX_P | GND   | GPIO[0]CLK_R<br>EQ | GPIO[11] | VIO_SD  | PDn     | GPIO(3)WLAN<br>IRQ(0) | SDIO DAT3         | SDIO DAT2 |                  | GND(G3)           |    |

|    |                     | 29         | 30           | 31             | 32      | 33      | 34          | 35    | 36        | 37        | 38      | 39      | 40       | 41    | 42                 | 43       | 44      | 45      | 46                    | 47                | 48        |                  |                   | -  |

AW-CM389NF Top View Pin Map

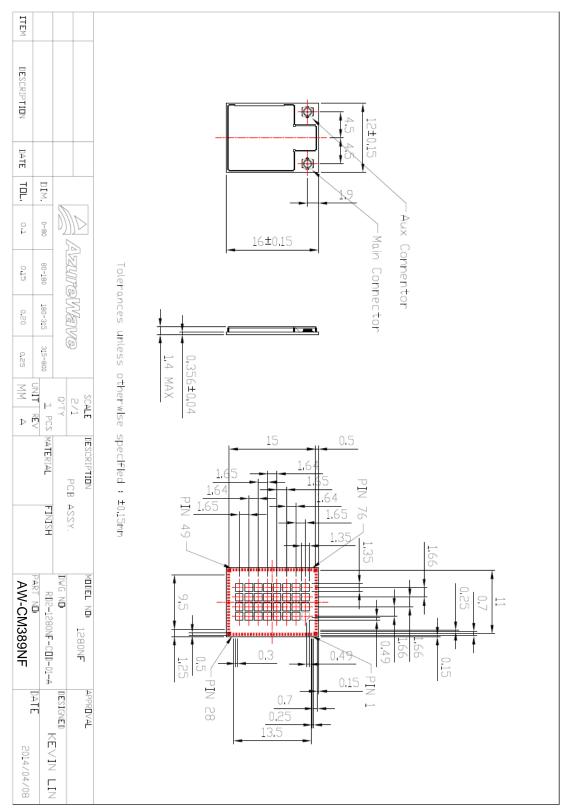

## 5. Mechanical Information

## 5-1. Package Outline Drawing

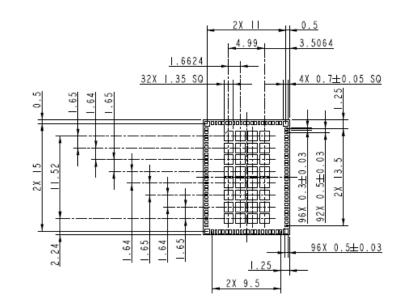

#### **5-2. Module Footprint**

## **AW-CM389NF PCB Layout Footprint**

<u>top view</u>

## 6. Package Information

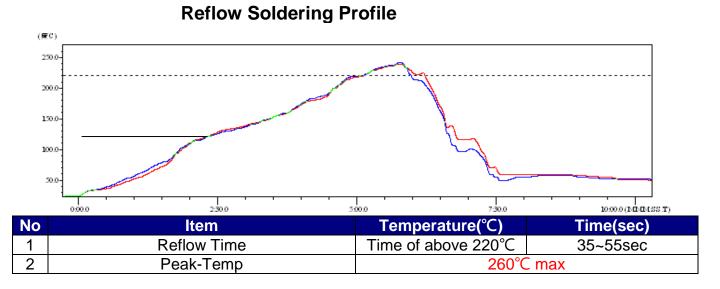

#### 6-1. Recommended Reflow Profile

Note:

- 1. Recommend to supply  $N_2$  for reflow oven

- 2. N<sub>2</sub> atmosphere during reflow (O<sub>2</sub><300ppm)

## 7. Shipping Information

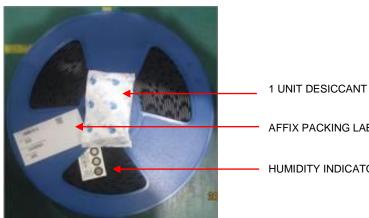

7-1

AFFIX PACKING LABEL

HUMIDITY INDICATOR CARD

#### 7-2

AFFIX PACKING LABEL

7-3

PINK BUBBLE WRAP

AFFIX PACKING LABEL

#### 7-5

1 Carton= 5 Boxes

Note: 1 tape reel = 1 box = 1,500pcs 1 carton = 5 boxes = 5 \* 1,500pcs=7,500pcs