# **AW-PU580**

# Wireless SMARC2.1 SoM

# **Datasheet**

Rev. D

**DF**

(For Standard)

#### **Features**

## **Arm Cortex-A53 MPCore platform**

- 32 KB L1 Instruction Cache

- 32 KB L1 Data Cache

- 512 KB unified L2 cache

- Media Processing Engine (MPE) with NEON technology supporting the Advanced Single Instruction Multiple Data architecture

- Floating Point Unit (FPU) with support of the VFPv4-D16 architecture

- Support of 64-bit Armv8-A architecture

## **Arm Cortex-M7 core platform**

- Low power operation

- Real-time processing

- 32 KB L1 Instruction Cache

- 32 KB L1 Data Cache

- 256 KB tightly coupled memory (TCM)

## **Image Sensor Processor (ISP)**

375 Mpixel/s HDR ISP supporting configurations, such as 12MP@30fps, 4kp45, or 2x 1080p80

# On board memory

- Ram : up to 6GB(48Gb) 32bit LPDDR4-4000 (support Inline ECC)

- Flash :16GB(128Gb) eMMC 5.1 (Optional)

# **Graphic Processing Unit**

- GC7000UL with OpenCL and Vulkan support

- 2 shader

- 166 million triangles/sec

- 1.0 giga pixel/sec

- 16 GFLOPs 32-bit

- Supports OpenGL ES 1.1, 2.0, 3.0, OpenCL 1.2, Vulkan

- Core clock frequency of 1000 MHz

- Shader clock frequency of 1000 MHz

- GC520L for 2D acceleration

## **Video Processing Unit**

- 1080p60 VP9 Profile 0, 2 (10-bit)

- 1080p60 HEVC/H.265 Main, Main 10 (up to level 5.1) decoder

- 1080p60 AVC/H.264 Baseline, Main, High decoder

- 1080p60 VP8 decoder

- 1080p60 AVC/H.264 encoder

- 1080p60 HEVC/H.265 encoder

# **Neutral Processing Unit (NPU)**

• 2.3 TOP/s Neural Network performance

#### HDMI 2.0a Tx

- Resolutions of: 720 x 480p60, 1280 x 720p60, 1920 x 1080p60, 1920 x 1080p120, 3840 x 2160p30

- Pixel clock up to 297 MHz

# **LCDIF Display Controller**

Support up to 1920x1200p60 display per LCDIF if no more than 2 instances used simultaneously, or 1x 1080p60 + 2x 720p60 if all 3 instances used simultaneously (one LCDIF drives MIPI DSI, one LCDIF drives LVDS Tx and one LCDIF drives HDMI Tx)

#### **MIPI Interface**

- 4-lane MIPI CSI interface

- 4-lane MIPI DSI interface

#### **Audio**

- S/PDIF input and output, including a new Raw Capture input mode

- Support I2S interface

## Connectivity

- 1x USB 3.0(or 1x USB 2.0 OTG) and 4x USB 2.0 One Ultra Secure Digital Host Controller (uSDHC) interface.

- SD/SDIO 3.0 compliance with 200 MHz SDR signaling to support up to 100MB/sec. Also support for SDXC (extended capacity)

- Two Gigabit Ethernet controller with support for Energy Efficient Ethernet (EEE), Ethernet AVB, and IEEE 1588.

- Three Universal Asynchronous Receiver / Transmitter (UART) modules.

- Four I2C modules.

- One ECSPI modules

- Two Controller Area Network (FlexCAN) modules, each optionally supporting flexible

data-rate (FD)

## **Security**

- Resource Domain Controller (RDC)

- Cortex®-A53 MPCore TrustZone® support

- On-chip RAM (OCRAM) secure region protection using OCRAM controller

- High Assurance Boot (HAB)

- Cryptographic Acceleration and Assurance Module (CAAM)

- Secure Non-Volatile Storage (SNVS)

- Optional Trust Platform Module (TPM 2.0)

#### WLAN + Bluetooth

- Wi-Fi 802.11 a/b/g/n/ac 2x2 (Wi-Fi 5)

- 2.4GHz and 5GHz Dual-Band

- Up to 866Mbps

- 20/40/80MHz channel bandwidth

- Bluetooth 5.3 (BR/ EDR/LE)

# **Revision History**

Document NO: R2-3580-DST-01

| Version | Revision<br>Date | DCN NO.   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Initials       | Approved        |

|---------|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|

| Α       | 2020/12/23       | DCN019724 | Draft version                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Steven<br>Jian | Chihhao<br>Liao |

| В       | 2021/04/15       | DCN021212 | <ul> <li>Removed SER0 &amp; PCIE_A</li> <li>Updated 1.2 Block Diagram</li> <li>Updated 2.2.1 Module Pin Table</li> <li>Added 3.5 Boot mode configuration</li> <li>Changed document format</li> <li>Updated 1.3.1 General</li> <li>Updated 1.3.2 Operating Conditions</li> <li>Updated 4.1 Mechanical Drawing</li> </ul>                                                                                                                                                   | Steven<br>Jian | Chihhao<br>Liao |

| С       | 2023/02/08       | DCN028617 | <ul> <li>Updated P134 P135 P140 P141 S4 P62 P67 P71 P74 P76 pin description</li> <li>Updated 2.2.2 CSI Feature Connector Pin Table (optional)</li> <li>Updated 1.2 Block Diagram</li> <li>Support Bluetooth 5.3</li> <li>Added I2C pull-ups info in 2.2.1 Module Pin Table</li> <li>Remove Wi-Fi BT Specs in 1.3 Specifications Table</li> <li>Updated 3.6 Power Consumption, 2.1 Pin Map, 4. Mechanical Information</li> <li>Added 1.1.1 Ordering Information</li> </ul> | Steven<br>Jian | Chihhao<br>Liao |

| D       | 2023/04/18       | DCN029047 | <ul> <li>Updated 1.1.1 Ordering Information</li> <li>Updated 1.2 Block Diagram</li> <li>Updated Ethernet and weight in 1.3.1 General</li> <li>Updated CSI description in 2.1 Pin Map and 2.2.2 CSI Feature Connector Pin Table (optional)</li> <li>Updated footnotes of Table 10 Master mode SAI timing (50 MHz)Table 12 Slave mode SAI timing (50 MHz)</li> </ul>                                                                                                        | Steven<br>Jian | Chihhao<br>Liao |

# **Table of Contents**

| Revision History                                                    | 4  |

|---------------------------------------------------------------------|----|

| 1. Introduction                                                     | 6  |

| 1.1 Product Overview                                                | 6  |

| 1.1.1 Ordering Information                                          | 7  |

| 1.2 Block Diagram                                                   |    |

| 1.3 Specifications Table                                            | 9  |

| 1.3.1 General                                                       | 9  |

| 1.3.2 Operating Conditions                                          | 10 |

| 2. Pin Definition                                                   | 11 |

| 2.1 Pin Map                                                         | 11 |

| 2.2 Pin Table                                                       | 12 |

| 2.2.1 Module Pin Table                                              | 12 |

| 2.2.2 CSI Feature Connector Pin Table (optional)                    | 26 |

| 3. Electrical Characteristics                                       | 27 |

| 3.1 Absolute Maximum Ratings                                        | 27 |

| 3.2 Recommended Operating Conditions                                | 27 |

| 3.3 GPIO DC Characteristics                                         | 28 |

| 3.4 Interface                                                       | 29 |

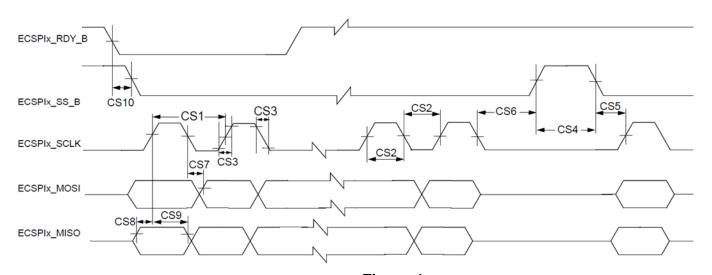

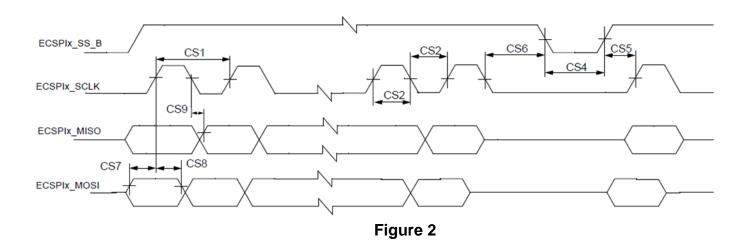

| 3.4.1 ECSPI timing parameters                                       | 29 |

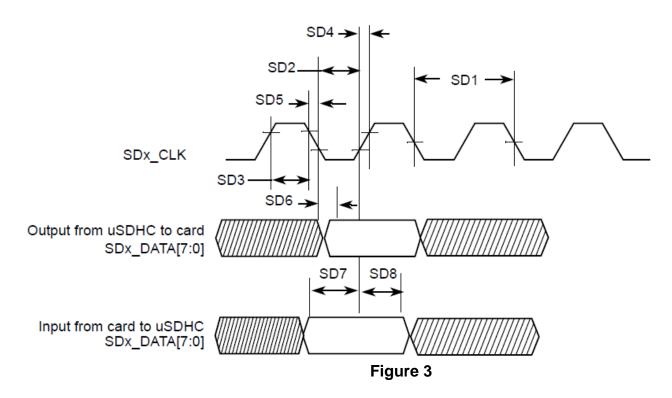

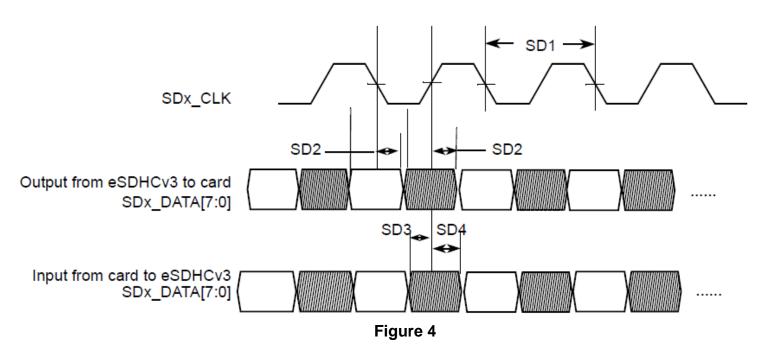

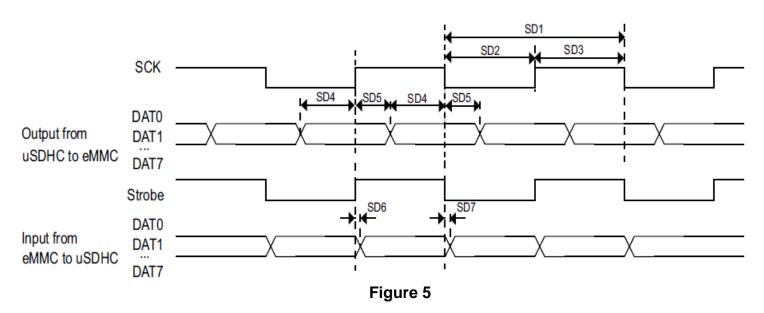

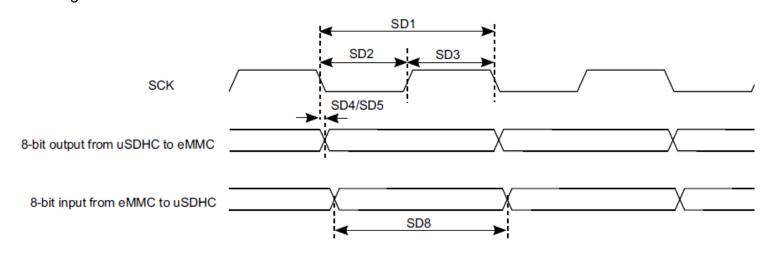

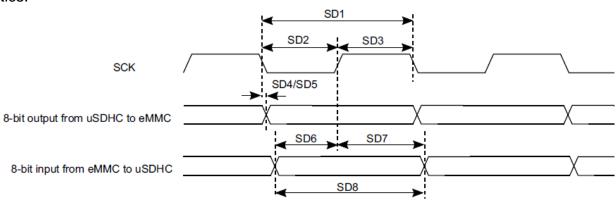

| 3.4.2 Ultra-high-speed SD/SDIO/MMC host interface (uSDHC) AC timing | 32 |

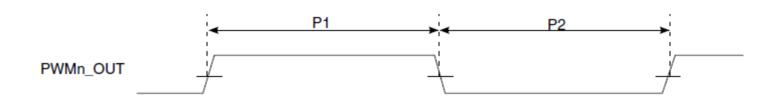

| 3.4.3 Pulse width modulator (PWM) timing parameters                 | 38 |

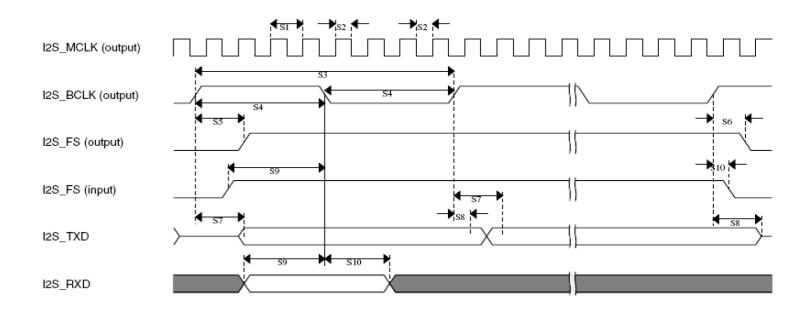

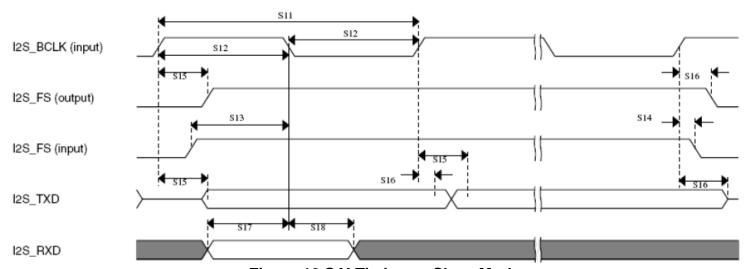

| 3.4.4 SAI/I2S switching specifications                              | 38 |

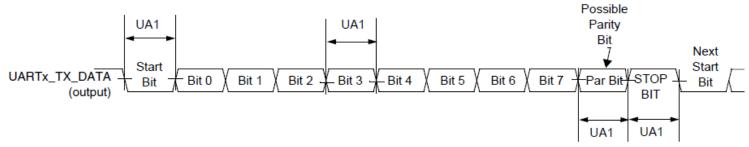

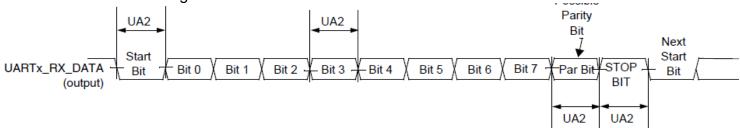

| 3.4.5 UART I/O configuration and timing parameters                  | 42 |

| 3.5 Boot mode configuration                                         | 45 |

| 3.6 Power Consumption                                               | 46 |

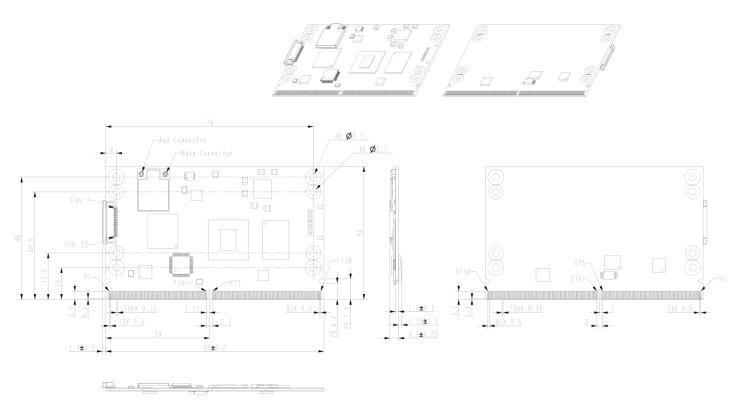

| 4. Mechanical Information                                           | 47 |

| 4.1 Mechanical Drawing                                              | 47 |

| 5. Packaging Information                                            | 48 |

#### 1. Introduction

#### 1.1 Product Overview

AzureWave Technologies, Inc. introduces the System on Module with SMARC ("Smart Mobility ARChitecture") 2.1 short size form factor & pin definition--- AW-PU580. By using AW-PU580, the customers can easily enable smart city, smart home, smart world and industrial IoT applications with the benefits of high design flexibility, short development cycle, and quick time-to-market.

The main system CPU shines in machine learning, vision, advanced multimedia and industrial IoT applications. The Neural Processing Unit (NPU) with 2.3 TOPS computing performance delivers substantially higher performance for Machine Learning tasks at nodes that removes cloud dependency and preserves individual privacy while providing a superior user experience. The integrated Image Signal Processor (ISP) brings real-time image processing to high-definition video and performs algorithms that extract the maximum image details in high-contrast scenes. The state-of-the-art Video Processing Unit (VPU), Graphics Processing Unit (GPU) and HIFi4 DSP enhance the multimedia experience. A dual gigabit Ethernet, one supporting Time-sensitive networking (TSN) provides control loops with highly precise timing. The CPU includes error correction code (ECC) in critical points of the system, including the DDR interface, for high system and security reliability and the required safety industrial level certification (SIL). Security protection features such as secure boot, encrypted boot, hardware firewall and run-time integrity checker (RTIC) support the prevention of multiple security attacks.

AW-PU580 adopts NXP's latest highly-integrated dual-band WLAN & Bluetooth SoC---88W8997. It supports IEEE 802.11ac/a/b/g/n 2X2 MU-MIMO WLAN and Bluetooth 5.3 (Core Standard) + Bluetooth 2.1+Enhanced Data Rate (EDR). With multiple wired and wireless interfaces, the AW-PU580 enables ubiquitous connectivity effortlessly.

# 1.1.1 Ordering Information

#### Planned versions:

| Model Name                 | Main Chip                            |            |     | Part Differentiator                                                    |

|----------------------------|--------------------------------------|------------|-----|------------------------------------------------------------------------|

| 4 I UAAZ VV VVI            | MIMX8ML8CVNKZAB<br>1.6GHz Industrial |            |     | 32MB NOR Flash, w/ WIFI, Ethernet x2, w/ TPM, w/ USB HUB, -40° ~85°    |

| AW-PU580-8CA-<br>4NAXX1XXC | MIMX8ML8CVNKZAB<br>1.6GHz Industrial | LPDDR4 4GB | N/A | w/o NOR Flash, w/o WIFI, Ethernet x1,<br>w/o TPM, w/o USB HUB, 0° ~60° |

#### AW-PU580 Option P/N

| A₩ | - | PU580 | - | 8CA | - | 4 | 16 | Α | A | 2 | W | W | Ι |

|----|---|-------|---|-----|---|---|----|---|---|---|---|---|---|

| A₩ | - | PU580 | - | 8CA |   | 4 | NA | X | X | 1 | X | X | С |

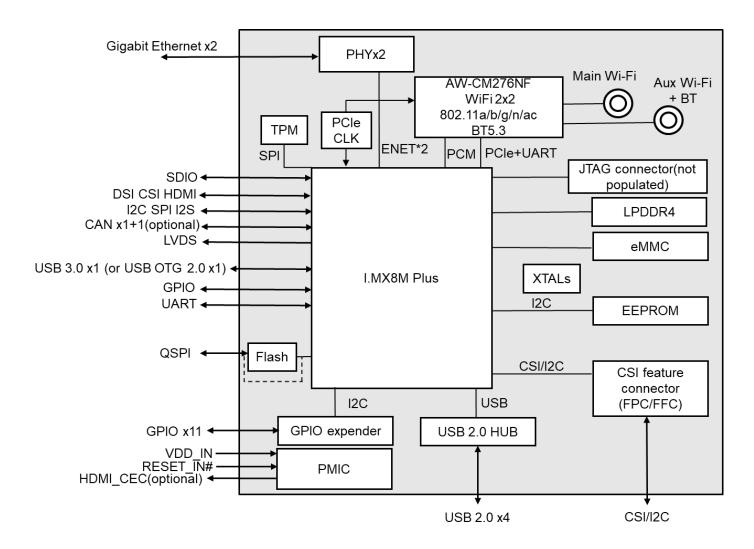

## 1.2 Block Diagram

<sup>\*</sup>Support different HW configurations. Please contact Azurewave for the details.

# 1.3 Specifications Table

### 1.3.1 General

| Features              | Description                                                                                                                                                                      |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Description   | Wireless SMARC2.1 SoM                                                                                                                                                            |

| Major Chipset         | NXP i.MX 8M Plus                                                                                                                                                                 |

| CPU Speed (frequency) | Up to 1.8GHz                                                                                                                                                                     |

| Wireless Connectivity | <ul> <li>Use the AW-CM267NF module*</li> <li>IEEE 802.11a/b/g/n/ac Wireless LAN 2T2R and Bluetooth 5.3</li> <li>RF Connector: I-PEX MHF4 Connector Receptacle (20449)</li> </ul> |

| USB                   | USB 3.0 x1(or USB 2.0 OTG x1) + USB2.0 x4                                                                                                                                        |

| uSDHC                 | x1 Ultra Secure Digital Host Controller (uSDHC) interfaces                                                                                                                       |

| Ethernet              | x2 Gigabit Ethernet controller: - GBE1 support Energy Efficient Ethernet (EEE),Ethernet AVB, and IEEE 1588 - GBE0 support TSN in addition to EEE, Ethernet AVB, and IEEE 1588    |

| MIPI Interface        | <ul><li>4-lane MIPI CSI interface</li><li>4-lane MIPI DSI interface</li></ul>                                                                                                    |

| UART                  | UART 4wire up to 1x + UART 2wire*2                                                                                                                                               |

| ECSPI                 | x1 ECSPI modules                                                                                                                                                                 |

| I <sup>2</sup> C      | x5 I <sup>2</sup> C modules                                                                                                                                                      |

| Audio Interface       | HDMI eARC     x2 I2S interfaces                                                                                                                                                  |

| Ram                   | Up to 6GB(48Gb) 32bit LPDDR4-4000(support Inline ECC)                                                                                                                            |

| Flash                 | 16GB(128Gb) eMMC 5.1 (Option)                                                                                                                                                    |

| Dimension             | 82mm x 50mm x 5.1mm                                                                                                                                                              |

| Form factor           | SMARC 2.1 short size                                                                                                                                                             |

| Weight                | 18.7 g                                                                                                                                                                           |

<sup>\*</sup>Note: For the detail, please refer to the data sheet of AW-CM276NF

# 1.3.2 Operating Conditions

| Features                 | Description                                                                                |

|--------------------------|--------------------------------------------------------------------------------------------|

| Operating Conditions     |                                                                                            |

| Voltage                  | VBAT: 3V to 5.25V (5V typical)                                                             |

| Operating<br>Temperature | Commercial grade: 0°C to 70°C <sup>1</sup><br>Industrial grade: -40°C to 85°C <sup>1</sup> |

| Operating Humidity       | less than 85%R.H.                                                                          |

| Storage Temperature      | -40°C to 85°C                                                                              |

| Storage Humidity         | less than 60%R.H.                                                                          |

| ESD Protection           |                                                                                            |

| Human Body Model         | N/A                                                                                        |

| Changed Device Model     | N/A                                                                                        |

$<sup>^1\,</sup>$  Based on the operating temperature grade of the SMARC components and the cooling performance.  $^2\,$  The Wi-Fi module operating temperature is only -30°C to 85°C.

# 2. Pin Definition

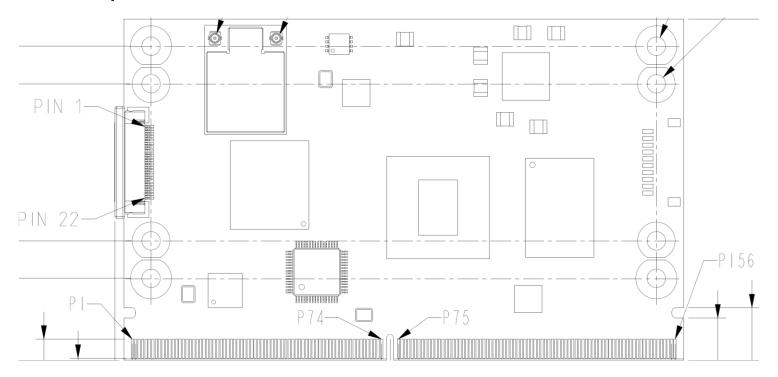

# 2.1 Pin Map

FORM NO.: FR2-015\_ A

Responsible Department: WBU

**Expiry Date: Forever**

### 2.2 Pin Table

## 2.2.1 Module Pin Table

| Pin No     | Definition     | Basic Description                                                                                                                                         | Voltage | Туре   |

|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| S38        | AUDIO_MCK      | Master Clock Output to I2S Codec(s)                                                                                                                       | 1.8V    | O CMOS |

| S156       | BATLOW#        | Battery low indication to Module. Carrier to float the line in inactive state.                                                                            | 1.8-5V  | I      |

| P123       | BOOT_SEL0#     | IMX8MP BOOT mode select BOOT_MODE0. 10 K ohms internal pull up                                                                                            | 1.8V    | I      |

| P124       | BOOT_SEL1#     | IMX8MP BOOT mode select BOOT_MODE1. 10 K ohms internal pull up                                                                                            | 1.8V    | I      |

| P125       | BOOT_SEL2#     | IMX8MP BOOT mode select BOOT_MODE2. 100 K ohms internal pull down                                                                                         | 1.8V    | I      |

| S6         | CAM_MCK        | Master clock output. Connect to SMARC MIPI-CSI Feature Connector Pin 22 internally.                                                                       | 1.8V    | 0      |

| P144       | CAN0_RX        | CAN Port 0 Receive Input (optional)                                                                                                                       | 1.8V    | I CMOS |

| P143       | CAN0_TX        | CAN Port 0 Transmit Output (optional)                                                                                                                     | 1.8V    | O CMOS |

| P146       | CAN1_RX        | CAN Port 1 Receive Input                                                                                                                                  | 1.8V    | I CMOS |

| P145       | CAN1_TX        | CAN Port 1 Transmit Output                                                                                                                                | 1.8V    | O CMOS |

| S154       | CARRIER_PWR_ON | Carrier Board circuits (apart from power management and power path circuits) should not be powered up until the Module asserts the CARRIER_PWR_ON signal. | 1.8V    | 0      |

| S153       | CARRIER_STBY#  | The Module shall drive this signal low when the system is in a standby power state.                                                                       | 1.8V    | 0      |

| S152       | CHARGER_PRSNT# | Held low by Carrier if DC input for battery charger is present.                                                                                           | 1.8-5V  | I      |

| S151       | CHARGING#      | Held low by Carrier during battery charging. Carrier to float the line when charge is complete.                                                           | 1.8-5V  | I      |

| S9         | CSI0_CK-       | Differential input (point to point). Use MIPI-CSI Feature Connector instead of the SMARC 2.0 CSI0 pin for 4 lane operation                                |         | I      |

| S8         | CSI0_CK+       | Differential input (point to point). Use MIPI-CSI Feature Connector instead of the SMARC 2.0 CSI0 pin for 4 lane operation                                |         | I      |

| <b>S12</b> | CSI0_RX0-      | Differential input (point to point). Use MIPI-CSI Feature Connector instead of the SMARC 2.0 CSI0 pin for 4 lane operation                                |         | I      |

| S11        | CSI0_RX0+      | Differential input (point to point). Use MIPI-CSI Feature Connector instead of the SMARC 2.0 CSI0 pin for 4 lane operation                                |         | I      |

| S15        | CSI0_RX1-      | Differential input (point to point). Use MIPI-CSI Feature Connector instead of the SMARC 2.0 CSI0 pin for 4 lane operation                                |         | I      |

| S14  | CSI0_RX1+      | Differential input (point to point). Use MIPI-CSI Feature Connector instead of the SMARC 2.0 CSI0 pin for 4 lane operation                                                                                                                                 |      | I   |

|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| P4   | CSI1_CK-       | CSI1 differential clock input (point to point)                                                                                                                                                                                                             |      | I   |

| Р3   | CSI1_CK+       | CSI1 differential clock input (point to point)                                                                                                                                                                                                             |      | I   |

| P8   | CSI1_RX0-      | CSI1 differential input (point to point)                                                                                                                                                                                                                   |      | I   |

| P7   | CSI1_RX0+      | CSI1 differential input (point to point)                                                                                                                                                                                                                   |      | I   |

| P11  | CSI1_RX1-      | CSI1 differential input (point to point)                                                                                                                                                                                                                   |      | I   |

| P10  | CSI1_RX1+      | CSI1 differential input (point to point)                                                                                                                                                                                                                   |      | I   |

| P14  | CSI1_RX2-      | CSI1 differential input (point to point)                                                                                                                                                                                                                   |      | I   |

| P13  | CSI1_RX2+      | CSI1 differential input (point to point)                                                                                                                                                                                                                   |      | I   |

| P17  | CSI1_RX3-      | CSI1 differential input (point to point)                                                                                                                                                                                                                   |      | Ι   |

| P16  | CSI1_RX3+      | CSI1 differential input (point to point)                                                                                                                                                                                                                   |      | I   |

| S135 | DSI0_CLK-      | Primary DSI Panel Differential Pair Clock Lines                                                                                                                                                                                                            |      | 0   |

| S134 | DSI0_CLK+      | Primary DSI Panel Differential Pair Clock Lines                                                                                                                                                                                                            |      | 0   |

| S126 | DSI0_D0-       | Primary DSI Panel Differential Pair Data Lines                                                                                                                                                                                                             |      | I/O |

| S125 | DSI0_D0+       | Primary DSI Panel Differential Pair Data Lines                                                                                                                                                                                                             |      | I/O |

| S129 | DSI0_D1-       | Primary DSI Panel Differential Pair Data Lines                                                                                                                                                                                                             |      | 0   |

| S128 | DSI0_D1+       | Primary DSI Panel Differential Pair Data Lines                                                                                                                                                                                                             |      | 0   |

| S132 | DSI0_D2-       | Primary DSI Panel Differential Pair Data Lines                                                                                                                                                                                                             |      | 0   |

| S131 | DSI0_D2+       | Primary DSI Panel Differential Pair Data Lines                                                                                                                                                                                                             |      | 0   |

| S138 | DSI0_D3-       | Primary DSI Panel Differential Pair Data Lines                                                                                                                                                                                                             |      | 0   |

| S137 | DSI0_D3+       | Primary DSI Panel Differential Pair Data Lines                                                                                                                                                                                                             |      | 0   |

| S155 | FORCE_RECOV#   | Low on this pin allows nonprotected segments of Module boot device to be rewritten / restored from an external USB Host on Module USB0. The Module USB0 operates in Client Mode when in the Force Recovery function is invoked. Pulled high on the Module. | 1.8V | 1   |

| P25  | GBE0_LINK_ACT# | Link / Activity Indication LED Driven Low on Link (10, 100 or 1000 Mbps) Blinks on Activity                                                                                                                                                                | 3.3V | 0   |

| P21  | GBE0_LINK100#  | Link Speed Indication LED for GBE0 100Mbps                                                                                                                                                                                                                 | 3.3V | 0   |

| P22 | GBE0_LINK1000# | Link Speed Indication LED for GBE0 1000Mbps                                                                                                                                                                                                                        | 3.3V | 0   |

|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| P29 | GBE0_MDI0-     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| P30 | GBE0_MDI0+     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| P26 | GBE0_MDI1-     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| P27 | GBE0_MDI1+     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| P23 | GBE0_MDI2-     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| P24 | GBE0_MDI2+     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| P19 | GBE0_MDI3-     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| P20 | GBE0_MDI3+     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| S31 | GBE1_LINK_ACT# | Link / Activity Indication LED Driven Low on Link (10, 100 or 1000 Mbps) Blinks on Activity                                                                                                                                                                        | 3.3V | 0   |

| S19 | GBE1_LINK100#  | Link Speed Indication LED for GBE0 100Mbps                                                                                                                                                                                                                         | 3.3V | 0   |

| S22 | GBE1_LINK1000# | Link Speed Indication LED for GBE0 1000Mbps                                                                                                                                                                                                                        | 3.3V | 0   |

| S18 | GBE1_MDI0-     | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations |      | I/O |

| S17  | GBE1_MDI0+ | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations | I/O    |

|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| S21  | GBE1_MDI1- | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations | I/O    |

| S20  | GBE1_MDI1+ | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations | I/O    |

| S24  | GBE1_MDI2- | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations | I/O    |

| S23  | GBE1_MDI2+ | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations | I/O    |

| S27  | GBE1_MDI3- | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations | I/O    |

| S26  | GBE1_MDI3+ | Differential Pair Signals for External Transformer Carrier Series Termination: Magnetics Module appropriate for 10/100/1000 GBE transceivers Carrier Parallel Termination: Secondary side center tap terminations appropriate for Gigabit Ethernet implementations | I/O    |

| P100 | GND_P100   | Ground                                                                                                                                                                                                                                                             | Ground |

| P103 | GND_P103   | Ground                                                                                                                                                                                                                                                             | Ground |

| P12  | GND_P12    | Ground                                                                                                                                                                                                                                                             | Ground |

| P120 | GND_P120   | Ground                                                                                                                                                                                                                                                             | Ground |

| P133 | GND_P133   | Ground                                                                                                                                                                                                                                                             | Ground |

| P142 | GND_P142   | Ground                                                                                                                                                                                                                                                             | Ground |

| P15  | GND_P15    | Ground                                                                                                                                                                                                                                                             | Ground |

| P18  | GND_P18    | Ground                                                                                                                                                                                                                                                             | Ground |

| P2   | GND_P2     | Ground                                                                                                                                                                                                                                                             | Ground |

|      |            | <del></del>                                                                                                                                                                                                                                                        |        |

|             | Azurevvave recir | nelogico, me. |        |

|-------------|------------------|---------------|--------|

| P32         | GND_P32          | Ground        | Ground |

| P38         | GND_P38          | Ground        | Ground |

| P47         | GND_P47          | Ground        | Ground |

| P50         | GND_P50          | Ground        | Ground |

| P53         | GND_P53          | Ground        | Ground |

| P59         | GND_P59          | Ground        | Ground |

| P68         | GND_P68          | Ground        | Ground |

| P79         | GND_P79          | Ground        | Ground |

| P82         | GND_P82          | Ground        | Ground |

| P85         | GND_P85          | Ground        | Ground |

| P88         | GND_P88          | Ground        | Ground |

| Р9          | GND_P9           | Ground        | Ground |

| P91         | GND_P91          | Ground        | Ground |

| P94         | GND_P94          | Ground        | Ground |

| P97         | GND_P97          | Ground        | Ground |

| S10         | GND_S10          | Ground        | Ground |

| S101        | GND_S101         | Ground        | Ground |

| S110        | GND_S110         | Ground        | Ground |

| S119        | GND_S119         | Ground        | Ground |

| S124        | GND_S124         | Ground        | Ground |

| S13         | GND_S13          | Ground        | Ground |

| S130        | GND_S130         | Ground        | Ground |

| S136        | GND_S136         | Ground        | Ground |

| S143        | GND_S143         | Ground        | Ground |

| S158        | GND_S158         | Ground        | Ground |

| <b>S</b> 16 | GND_S16          | Ground        | Ground |

| -           | •                |               |        |

|      | Azurewave recir   | nologico, me.           |      |        |

|------|-------------------|-------------------------|------|--------|

| S25  | GND_S25           | Ground                  |      | Ground |

| S3   | GND_S3            | Ground                  |      | Ground |

| S34  | GND_S34           | Ground                  |      | Ground |

| S47  | GND_S47           | Ground                  |      | Ground |

| S61  | GND_S61           | Ground                  |      | Ground |

| S64  | GND_S64           | Ground                  |      | Ground |

| S67  | GND_S67           | Ground                  |      | Ground |

| S70  | GND_S70           | Ground                  |      | Ground |

| S73  | GND_S73           | Ground                  |      | Ground |

| S80  | GND_S80           | Ground                  |      | Ground |

| S83  | GND_S83           | Ground                  |      | Ground |

| S86  | GND_S86           | Ground                  |      | Ground |

| S89  | GND_S89           | Ground                  |      | Ground |

| S92  | GND_S92           | Ground                  |      | Ground |

| P108 | GPIO0 / CAM0_PWR# | GPIO                    | 1.8V | I/O    |

| P109 | GPIO1 / CAM1_PWR# | GPIO                    | 1.8V | I/O    |

| P118 | GPIO10            | GPIO                    | 1.8V | I/O    |

| P119 | GPIO11            | GPIO                    | 1.8V | I/O    |

| S142 | GPIO12            | GPIO                    | 1.8V | I/O    |

| S123 | GPIO13            | GPIO                    | 1.8V | I/O    |

| P110 | GPIO2 / CAM0_RST# | GPIO                    | 1.8V | I/O    |

| P111 | GPIO3 / CAM1_RST# | GPIO                    | 1.8V | I/O    |

| P112 | GPIO4 / HDA_RST#  | GPIO                    | 1.8V | I/O    |

| P113 | GPIO5 / PWM_OUT   | GPIO5 PWM capability    | 1.8V | I/O    |

| P114 | GPIO6 / TACHIN    | GPIO6 Tachin capability | 1.8V | I/O    |

| P115 | GPIO7             | GPIO                    | 1.8V | I/O    |

| ·    | •                 |                         |      | J      |

| P116       | GPIO8                                                                                                                                                           | GPIO                                                                                                                                              | 1.8V | I/O      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|

| P117       | GPIO9                                                                                                                                                           | GPIO                                                                                                                                              | 1.8V | I/O      |

| S53        | HDA_CK / I2S2_CK                                                                                                                                                | I2S2 Digital Audio Clock. Floating if CAN0_RX is used                                                                                             | 1.8V | I/O CMOS |

| S52        | HDA_SDI / I2S2_SDIN                                                                                                                                             | I2S2 Digital Audio Input                                                                                                                          | 1.8V | I CMOS   |

| S51        | HDA_SDO /<br>I2S2_SDOUT                                                                                                                                         | I2S2 Digital Audio Output                                                                                                                         | 1.8V | O CMOS   |

| S50        | HDA_SYNC /<br>I2S2_LRCK                                                                                                                                         | 2S2 Left & Right Synchronization Clock. Floating if CAN0_TX s used                                                                                |      | I/O CMOS |

| P102       | HDMI_CK-                                                                                                                                                        | HDMI Port, Differential Pair Clock Lines                                                                                                          |      | 0        |

| P101       | HDMI_CK+                                                                                                                                                        | CK+ HDMI Port, Differential Pair Clock Lines                                                                                                      |      | 0        |

| P105       | HDMI_CTRL_CK                                                                                                                                                    | DMI_CTRL_CK I2C_CLK Line Dedicated to HDMI                                                                                                        |      | I/O      |

| P106       | HDMI_CTRL_DAT                                                                                                                                                   | HDMI_CTRL_DAT I2C_DAT Line Dedicated to HDMI                                                                                                      |      | I/O      |

| P99        | HDMI_D0-                                                                                                                                                        | HDMI Port, Differential Pair Data Lines                                                                                                           |      | 0        |

| P98        | HDMI_D0+                                                                                                                                                        | HDMI Port, Differential Pair Data Lines                                                                                                           |      | 0        |

| P96        | HDMI_D1-                                                                                                                                                        | HDMI Port, Differential Pair Data Lines                                                                                                           |      | 0        |

| P95        | HDMI_D1+                                                                                                                                                        | HDMI_D1+ HDMI Port, Differential Pair Data Lines                                                                                                  |      | 0        |

| P93        | HDMI_D2-                                                                                                                                                        | HDMI Port, Differential Pair Data Lines                                                                                                           |      | 0        |

| P92        | HDMI_D2+                                                                                                                                                        | HDMI Port, Differential Pair Data Lines                                                                                                           |      | 0        |

| P104       | HDMI_HPD                                                                                                                                                        | HDMI Hot Plug Active High Detection Signal that Serves as an Interrupt Request                                                                    | 1.8V | I        |

| S5         | I2C_CAM0_CK                                                                                                                                                     | CAM0 I2C clock for serial camera data support link. Connect to SMARC MIPI-CSI Feature Connector Pin 19 internally. With PU 4.7k ohms on module.   | 1.8V | I/O      |

| <b>S</b> 7 | I2C_CAM0_DAT                                                                                                                                                    | CAM0 I2C data for serial camera data support link. Connect to SMARC MIPI-CSI Feature Connector Pin 20 internally. With PU 4.7k ohms on module.    | 1.8V | I/O      |

| <b>S</b> 1 | I2C_CAM1_CK                                                                                                                                                     | CAM1 I2C clock for serial camera data support link. I2C address 0x68(1101000x) is used by internal PCIe clock source With PU 4.7k ohms on module. | 1.8V | I/O      |

| S2         | CAM1 I2C data for serial camera data support link. I2C  I2C_CAM1_DAT address 0x68(1101000x) is used by internal PCIe clock source  With PU 4.7k ohms on module. |                                                                                                                                                   | 1.8V | I/O      |

| S48        | I2C_GP_CK                                                                                                                                                       | General Purpose I2C Clock Signal. I2C address                                                                                                     |      | I/O      |

| S49        | I2C_GP_DAT                                                                                                                                                      | General Purpose I2C Data Signal. I2C address 0x50(1010000x) is used by internal EEPROM With PU 4.7k ohms on module.                               | 1.8V | I/O      |

| S139 | I2C_LCD_CK                                                                                                                                                                                                                     | DDC Clock Line Used for Flat Panel Detection and Control. I2C address 0x25(0100101x) is used by internal PMIC With PU 4.7k ohms on module. | 1.8V   | I/O      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|

| S140 | I2C_LCD_DAT                                                                                                                                                                                                                    | DDC Data Line Used for Flat Panel Detection and Control. I2C address 0x25(0100101x) is used by internal PMIC With PU 4.7k ohms on module.  | 1.8V   | I/O      |

| P121 | I2C_PM_CK                                                                                                                                                                                                                      | Power management I2C bus CLK. With PU 2.2k ohms on module.                                                                                 | 1.8V   | I/O      |

| P122 | I2C_PM_DAT                                                                                                                                                                                                                     | Power management I2C bus DATA With PU 2.2k ohms on module.                                                                                 | 1.8V   | I/O      |

| S42  | I2S0_CK                                                                                                                                                                                                                        | I2S0 Digital Audio Clock                                                                                                                   | 1.8V   | I/O CMOS |

| S39  | I2S0_LRCK                                                                                                                                                                                                                      | I2S0 Left & Right Synchronization Clock                                                                                                    | 1.8V   | I/O CMOS |

| S41  | I2S0_SDIN                                                                                                                                                                                                                      | I2S0 Digital Audio Input                                                                                                                   | 1.8V   | I CMOS   |

| S40  | I2S0_SDOUT I2S0 Digital Audio Output                                                                                                                                                                                           |                                                                                                                                            | 1.8V   | O CMOS   |

| S127 | LCD0_BKLT_EN Primary Panel Backlight Enable                                                                                                                                                                                    |                                                                                                                                            | 1.8V   | 0        |

| S141 | LCD0_BKLT_PWM Primary Panel Brightness Control                                                                                                                                                                                 |                                                                                                                                            | 1.8V   | 0        |

| S133 | LCD0_VDD_EN                                                                                                                                                                                                                    | -                                                                                                                                          |        | 0        |

| S148 | Lid open/close indication to Module. Low indicates lid closure (which system may use to initiate a sleep state). Carrier to float the line in inactive state. Active low, level sensitive. Should be de-bounced on the Module. |                                                                                                                                            | 1.8-5V | I        |

| S112 | LVDS1_0-                                                                                                                                                                                                                       | Secondary LVDS Channel Differential Pair Data Lines                                                                                        |        | 0        |

| S111 | LVDS1_0+                                                                                                                                                                                                                       | Secondary LVDS Channel Differential Pair Data Lines                                                                                        |        | 0        |

| S115 | LVDS1_1-                                                                                                                                                                                                                       | Secondary LVDS Channel Differential Pair Data Lines                                                                                        |        | 0        |

| S114 | LVDS1_1+                                                                                                                                                                                                                       | Secondary LVDS Channel Differential Pair Data Lines                                                                                        |        | 0        |

| S118 | LVDS1_2-                                                                                                                                                                                                                       | Secondary LVDS Channel Differential Pair Data Lines                                                                                        |        | 0        |

| S117 | LVDS1_2+                                                                                                                                                                                                                       | Secondary LVDS Channel Differential Pair Data Lines                                                                                        |        | 0        |

| S121 | LVDS1_3-                                                                                                                                                                                                                       | Secondary LVDS Channel Differential Pair Data Lines                                                                                        |        | 0        |

| S120 | LVDS1_3+                                                                                                                                                                                                                       | Secondary LVDS Channel Differential Pair Data Lines                                                                                        |        | 0        |

| S109 | LVDS1_CK-                                                                                                                                                                                                                      | Secondary LVDS Channel Differential Pair Clock Lines                                                                                       |        | 0        |

| S108 | LVDS1_CK+                                                                                                                                                                                                                      | Secondary LVDS Channel Differential Pair Clock Lines                                                                                       |        | 0        |

| S106 | NC_DP0_AUX-                                                                                                                                                                                                                    | Floating Pin, No connect to anything.                                                                                                      |        | Floating |

| S95  | NC_DP0_AUX_SEL                                                                                                                                                                                                                 | Floating Pin, No connect to anything.                                                                                                      |        | Floating |

|      | NC_DP0_AUX+          | Floating Pin, No connect to anything. | Floating |

|------|----------------------|---------------------------------------|----------|

| 508  |                      | l                                     | و        |

| 390  | NC_DP0_HPD           | Floating Pin, No connect to anything. | Floating |

| S94  | NC_DP0_LANE0-        | Floating Pin, No connect to anything. | Floating |

| S93  | NC_DP0_LANE0+        | Floating Pin, No connect to anything. | Floating |

| S97  | NC_DP0_LANE1-        | Floating Pin, No connect to anything. | Floating |

| S96  | NC_DP0_LANE1+        | Floating Pin, No connect to anything. | Floating |

| S100 | NC_DP0_LANE2-        | Floating Pin, No connect to anything. | Floating |

| S99  | NC_DP0_LANE2+        | Floating Pin, No connect to anything. | Floating |

| S103 | NC_DP0_LANE3-        | Floating Pin, No connect to anything. | Floating |

| S102 | NC_DP0_LANE3+        | Floating Pin, No connect to anything. | Floating |

| P107 | NC_DP1_AUX_SEL       | Floating Pin, No connect to anything. | Floating |

| S144 | NC_eDP0_HPD          | Floating Pin, No connect to anything. | Floating |

| S113 | NC_eDP1_HPD          | Floating Pin, No connect to anything. | Floating |

| S43  | NC_ESPI_ALERT0#      | Floating Pin, No connect to anything. | Floating |

| S44  | NC_ESPI_ALERT1#      | Floating Pin, No connect to anything. | Floating |

| S58  | NC_ESPI_RESET#       | Floating Pin, No connect to anything. | Floating |

| P28  | NC_GBE0_CTREF        | Floating Pin, No connect to anything. | Floating |

| P6   | NC_GBE0_SDP          | Floating Pin, No connect to anything. | Floating |

| S28  | NC_GBE1_CTREF        | Floating Pin, No connect to anything. | Floating |

| P5   | NC_GBE1_SDP          | Floating Pin, No connect to anything. | Floating |

| S107 | NC_LCD1_BKLT_EN      | Floating Pin, No connect to anything. | Floating |

| SIZZ | NC_LCD1_BKLT_PW<br>M | Floating Pin, No connect to anything. | Floating |

| S116 | NC_LCD1_VDD_EN       | Floating Pin, No connect to anything. | Floating |

| S45  | NC_MDIO_CLK          | Floating Pin, No connect to anything. | Floating |

| S46  | NC_MDIO_DAT          | Floating Pin, No connect to anything. | Floating |

| P78  | NC_PCIE_A_CKREQ#     | Floating Pin, No connect to anything. | Floating |

| P84         | NC_PCIE_A_REFCK- | Floating Pin, No connect to anything. | Floating |

|-------------|------------------|---------------------------------------|----------|

| P83         | NC_PCIE_A_REFCK+ | Floating Pin, No connect to anything. | Floating |

| P75         | NC_PCIE_A_RST#   | Floating Pin, No connect to anything. | Floating |

| P87         | NC_PCIE_A_RX-    | Floating Pin, No connect to anything. | Floating |

| P86         | NC_PCIE_A_RX+    | Floating Pin, No connect to anything. | Floating |

| P90         | NC_PCIE_A_TX-    | Floating Pin, No connect to anything. | Floating |

| P89         | NC_PCIE_A_TX+    | Floating Pin, No connect to anything. | Floating |

| P77         | NC_PCIE_B_CKREQ# | Floating Pin, No connect to anything. | Floating |

| S85         | NC_PCIE_B_REFCK- | Floating Pin, No connect to anything. | Floating |

| S84         | NC_PCIE_B_REFCK+ | Floating Pin, No connect to anything. | Floating |

| S76         | NC_PCIE_B_RST#   | Floating Pin, No connect to anything. | Floating |

| S88         | NC_PCIE_B_RX-    | Floating Pin, No connect to anything. | Floating |

| S87         | NC_PCIE_B_RX+    | Floating Pin, No connect to anything. | Floating |

| S91         | NC_PCIE_B_TX-    | Floating Pin, No connect to anything. | Floating |

| S90         | NC_PCIE_B_TX+    | Floating Pin, No connect to anything. | Floating |

| P81         | NC_PCIE_C_REFCK- | Floating Pin, No connect to anything. | Floating |

| P80         | NC_PCIE_C_REFCK+ | Floating Pin, No connect to anything. | Floating |

| S77         | NC_PCIE_C_RST#   | Floating Pin, No connect to anything. | Floating |

| S79         | NC_PCIE_C_RX-    | Floating Pin, No connect to anything. | Floating |

| S78         | NC_PCIE_C_RX+    | Floating Pin, No connect to anything. | Floating |

| S82         | NC_PCIE_C_TX-    | Floating Pin, No connect to anything. | Floating |

| S81         | NC_PCIE_C_TX+    | Floating Pin, No connect to anything. | Floating |

| S33         | NC_PCIE_D_RX-    | Floating Pin, No connect to anything. | Floating |

| <b>S32</b>  | NC_PCIE_D_RX+    | Floating Pin, No connect to anything. | Floating |

| <b>S</b> 30 | NC_PCIE_D_TX-    | Floating Pin, No connect to anything. | Floating |

| S29         | NC_PCIE_D_TX+    | Floating Pin, No connect to anything. | Floating |

|             |                  | <del></del>                           |          |

| S146 | NC_PCIE_WAKE#                                      | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

|------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|

| S54  | NC_SATA_ACT#                                       | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P52  | NC_SATA_RX-                                        | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P51  | NC_SATA_RX+                                        | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P49  | NC_SATA_TX-                                        | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P48  | NC_SATA_TX+                                        | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P132 | NC_SER0_CTS#                                       | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P131 | NC_SER0_RTS# Floating Pin, No connect to anything. |                                                                                                                                                     |        | Floating |

| P130 | NC_SER0_RX                                         | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P129 | NC_SER0_TX                                         | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P31  | NC_SPI0_CS1#                                       | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P55  | NC_SPI1_CS1# /<br>ESPI_CS1# /<br>QSPI_CS1#         | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P64  | NC_USB0_OTG_ID                                     | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| S75  | NC_USB2_SSRX-                                      | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| S74  | NC_USB2_SSRX+                                      | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| S72  | NC_USB2_SSTX-                                      | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| S71  | NC_USB2_SSTX+                                      | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| S60  | NC_USB5-                                           | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| S55  | NC_USB5_EN_OC#                                     | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| S59  | NC_USB5+                                           | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| S147 | NC_VDD_RTC                                         | Floating Pin, No connect to anything.                                                                                                               |        | Floating |

| P128 | POWER_BTN#                                         | Power-button input from Carrier Board. Carrier to float the line in in-active state. Active low, level sensitive. Should be debounced on the Module | 1.8-5V | I        |

| P56  | QSPI_CK                                            | floating, if internal QSPI flash is used                                                                                                            | 1.8V   | O CMOS   |

| P54  | QSPI_CS0#                                          | floating, if internal QSPI flash is used                                                                                                            | 1.8V   | O CMOS   |

| P58  | QSPI_IO_0                                          | floating, if internal QSPI flash is used                                                                                                            | 1.8V   | I/O CMOS |

| P57     | QSPI_IO_1                                                                                                       | floating, if internal QSPI flash is used                                                               | 1.8V     | I/O CMOS |

|---------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------|----------|

| S56     | QSPI_IO_2                                                                                                       | floating, if internal QSPI flash is used                                                               | 1.8V     | I/O CMOS |

| S57     | QSPI_IO_3                                                                                                       | floating, if internal QSPI flash is used                                                               | 1.8V     | I/O CMOS |

| P127    | RESET_IN#                                                                                                       | Reset input from Carrier Board. Carrier drives low to force a Module reset, floats the line otherwise. | 1.8-5V   | I        |

| P126    | RESET_OUT#                                                                                                      | General purpose reset output to Carrier Board.                                                         | 1.8V     | 0        |

| P73     | RSVD_EARC_N_HPD                                                                                                 | EARC N HPD Out                                                                                         |          | 0        |

| P72     | RSVD_EARC_P_UTIL                                                                                                | EARC P UTIL Out                                                                                        |          | 0        |

| S4      | RSVD_PMIC_32K_OU<br>T_1V8_CEC                                                                                   | C_OU 32.768 CLK output from internal PMIC. Can be used for HDMI CEC pin (different HW option)          |          | 0        |

| P35     | SDIO_CD#                                                                                                        | SDIO Card Detect. This signal indicates when a SDIO/MMC                                                |          | I        |

| P36     | SDIO_CK SDIO Clock. With each cycle of this signal a one-bit transfer on the command and each data line occurs. |                                                                                                        | 1.8/3.3V | 0        |

| P34     | SDIO_CMD                                                                                                        | SDIO Command/Response. This signal is used for card                                                    |          | I/O      |

| P39     | SDIO_D0                                                                                                         | SDIO Data lines. These signals operate in push-pull mode.                                              |          | I/O      |

| P40     | SDIO_D1                                                                                                         | SDIO Data lines. These signals operate in push-pull mode.                                              |          | I/O      |

| P41     | SDIO_D2                                                                                                         | SDIO Data lines. These signals operate in push-pull mode.                                              | 1.8/3.3V | I/O      |

| P42     | SDIO_D3                                                                                                         | SDIO Data lines. These signals operate in push-pull mode.                                              | 1.8/3.3V | I/O      |

| P37     | SDIO_PWR_EN                                                                                                     | SDIO Power Enable. This signal is used to enable the power being supplied to a SD/MMC card device.     | 3.3V     | 0        |

| P33     | SDIO_WP                                                                                                         | SDIO Write Protect. This signal denotes the state of the write-protect tab on SD cards.                | 1.8/3.3V | I        |

| P135    | SER1_RX                                                                                                         | Asynchronous Serial Data Input Port 1. For A53 debug use by default                                    | 1.8V     | I        |

| P134    | SER1_TX                                                                                                         | Asynchronous Serial Data Output Port 1. For A53 debug use by default                                   | 1.8V     | 0        |

| P139    | SER2_CTS#                                                                                                       | Clear to Send Handshake Line for Port 1                                                                | 1.8V     | I        |

| P138    | SER2_RTS#                                                                                                       | Request to Send Handshake Line for Port 1                                                              | 1.8V     | 0        |

| P137    | SER2_RX                                                                                                         | Asynchronous Serial Data Input Port 2                                                                  |          | I        |

| P136    | SER2_TX                                                                                                         | Asynchronous Serial Data Output Port 2                                                                 |          | 0        |