# AW-NM372SM

# IEEE 802.11 b/g/n Wireless LAN and Bluetooth Module

## **Datasheet**

Rev. C

**0B**

(For Standard)

#### **Features**

- Integrates Infineon solutions of CYW43438 A1 Wi-Fi /BT/FM RX SoC

- SDIO v2.0 interfaces support for WLAN

- High speed UART and PCM for Bluetooth

- Lead-free Design

- 12.0mm(L) x 12.0mm(W) x 1.5 mm(H) 47 pin LGA package

- With Crystal(XTAL)

#### Wi-Fi

- Single band 2.4 GHz 802.11 b/g/n

- SDIO v2.0, including DS and HS modes

- Security-WEP, WPA/WPA2 (personal), AES (HW), TKIP (HW), CKIP (SW), WMM/WMM-PS/WMM-SA

- Dara Rate up to 72.2Mbps

#### **Bluetooth**

- Supports extended Synchronous Connections (eSCO), for enhanced voice quality by allowing for retransmission of dropped packets

- Adaptive Frequency Hopping (AFH) for reducing radio frequency interference

- Maximum UART baud rates up to 4 Mbps

- Supports 5.0's LE Secure Connections

- Supports Bluetooth Core Specification version

5.1 + (Enhanced Data Rate) EDR features:

- Adaptive Frequency Hopping (AFH)

- Quality of Service (QoS)

- Extended Synchronous Connections (eSCO) Voice Connections

- Fast Connect (interlaced page and inquiry scans)

- Secure Simple Pairing (SSP)

- Sniff Subrating (SSR)

- Encryption Pause Resume (EPR)

- Extended Inquiry Response (EIR)

- Link Supervision Timeout (LST)

- Interface support Host Controller Interface (HCI) using a high-speed UART interface and PCM for audio data

#### FΜ

- 76-MHz to 108-MHz FM bands supported (US, Europe, and Japan)

- RDS and RBDS demodulator and decoder with filter and buffering functions

- FM subsystem control using the Bluetooth HCl interface

- FM subsystem operates from reference clock inputs

- Improved audio interface capabilities with fullfeatured bidirectional PCM.

- Auto search and tuning functions

### **Revision History**

Document NO: R2-2372SM-DST-01

| Version | Revision<br>Date | DCN NO.   | Description                                                                                                                                                                    | Initials       | Approved        |

|---------|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|

| 0.1     | 2018/05/08       |           | Initial Version                                                                                                                                                                | Roger Lee      | Amos Fu         |

| 0.2     | 2018/11/20       |           | ● Updated 1.4.2                                                                                                                                                                | Chao Lee       | Amos Fu         |

| 0.3     | 2018/12/18       |           | Updated 1.4.2                                                                                                                                                                  | Chao Lee       | Amos Fu         |

| 0.4     | 2019/05/22       |           | <ul> <li>Updated 1.3 Block Diagram</li> <li>Updated 4.1 Mechanical<br/>Drawing</li> </ul>                                                                                      | Steven<br>Jian | Chihhao<br>Liao |

| 0.5     | 2019/07/15       |           | <ul> <li>Added 3.6 Host Interface<br/>Timing</li> <li>Added 3.7 Frequency<br/>References</li> </ul>                                                                            | Steven<br>Jian | Chihhao<br>Liao |

| 0.6     | 2019/09/02       |           | <ul> <li>Updated 1.4.4 Operating<br/>Conditions</li> </ul>                                                                                                                     | Steven<br>Jian | Chihhao<br>Liao |

| 0.7     | 2019/09/11       |           | <ul> <li>Updated 1.4.4 Operating<br/>Conditions</li> </ul>                                                                                                                     | Steven<br>Jian | Chihhao<br>Liao |

| Α       | 2020/03/04       | DCN016812 | <ul> <li>Changed Document format</li> <li>Updated 3.3 Digital IO Pin<br/>DC Characteristics</li> </ul>                                                                         | Steven<br>Jian | Chihhao<br>Liao |

| В       | 2020/06/08       | DCN017435 | <ul> <li>Updated 1.3.1 General</li> <li>Corrected Operating<br/>Temperature in 1.3.4<br/>Operating Conditions</li> <li>Support Bluetooth Core<br/>Specification 5.1</li> </ul> | Steven<br>Jian | Chihhao<br>Liao |

| С       | 2021/04/15       | DCN021181 | <ul> <li>Changed document format</li> <li>Updated the chip vendor name</li> </ul>                                                                                              | Steven<br>Jian | Chihhao<br>Liao |

#### **Table of Contents**

| Revision History                      | 3  |

|---------------------------------------|----|

| Table of Contents                     | 4  |

| 1. Introduction                       | 5  |

| 1.1 Product Overview                  | 5  |

| 1.2 Block Diagram                     | 6  |

| 1.3 Specifications Table              | 7  |

| 1.3.1 General                         | 7  |

| 1.3.2 WLAN                            | 7  |

| 1.3.3 Bluetooth                       | 8  |

| 1.3.4 Operating Conditions            | 9  |

| 2. Pin Definition                     |    |

| 2.1 Pin Map                           | 10 |

| 2.2 Pin Table                         | 11 |

| 3. Electrical Characteristics         | 14 |

| 3.1 Absolute Maximum Ratings          | 14 |

| 3.2 Recommended Operating Conditions  |    |

| 3.3 Digital IO Pin DC Characteristics |    |

| 3.4 Host Interface                    | 16 |

| 3.4.1 SDIO                            | 16 |

| 3.4.2 UART Interface                  | 18 |

| 3.4.3 PCM Interface Timing            | 20 |

| 3.5 Power up Timing Sequence          | 24 |

| 3.6 Frequency References              | 26 |

| 3.7 Power Consumption*                | 26 |

| 3.7.1 WLAN                            | 26 |

| 3.7.2 Bluetooth                       | 27 |

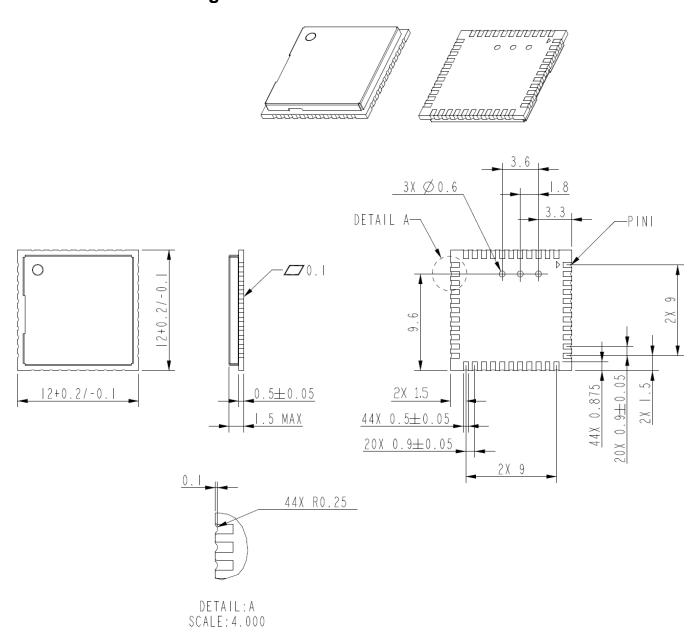

| 4. Mechanical Information             | 28 |

| 4.1 Mechanical Drawing                | 28 |

| 5. Packaging Information              | 29 |

#### 1. Introduction

#### 1.1 Product Overview

AzureWave Technologies, Inc. introduces the advanced IEEE 802.11 b/g/n WLAN and Bluetooth combo module - AW-NM372SM. The module is targeted to mobile and embedded devices which need small footprint package, low power consumption, and multiple OS support. The module supports 2.4GHz IEEE 802.11n MAC/baseband/radio, and Bluetooth 5.1 functionality. It also features an integrated Power Management Unit (PMU), Power Amplifiers (PAs), and a Low Noise Amplifier (LNA) to address the needs of mobile devices that require minimal power consumption and compact size. By using AW-NM372SM, the customers can easily enable the Wi-Fi and BT embedded applications with the benefits of high design flexibility, short development cycle, and quick time-to-market. Specified in the IEEE 802.11 standard minimize the system power requirements by using AW-NM372SM. In addition to the support of WPA/WPA2 (personal) and WEP encryption, the AW-NM372SM also supports the IEEE 802.11i security standard through AES and TKIP acceleration hardware for faster data encryption. For the video, voice and multimedia applications the AW-NM372SM support 802.11e Quality of Service (QoS). The host interface is SDIO v2.0 interface.

For Bluetooth operation, the AW-NM372SM is Bluetooth Core Specification 5.1 compliance. The Bluetooth transmitter also features a Class 1 power amplifier. The AW-NM372SM supports extended Synchronous Connections (eSCO), for enhanced voice quality by allowing for retransmission of dropped packets, and Adaptive Frequency Hopping (AFH) for reducing radio frequency interference. It also incorporates all Bluetooth 5.1 compliance features including secure simple pairing, sniff subrating, and encryption pause and resume and supports Bluetooth 5.1 compliance LE Secure Connections. An independent, high-speed UART is provided for the Bluetooth host interface. The Bluetooth subsystem presents a standard Host Controller Interface (HCI) via a high speed UART and PCM for audio.

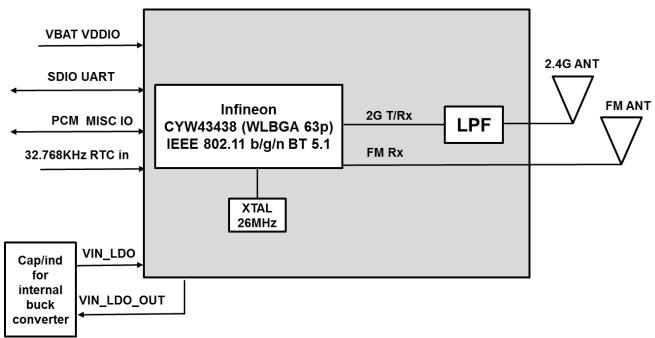

#### 1.2 Block Diagram

AW-NM372SM Block Diagram

#### 1.3 Specifications Table

#### 1.3.1 General

| Features                   | Description                                         |  |  |

|----------------------------|-----------------------------------------------------|--|--|

| <b>Product Description</b> | IEEE 802.11 b/g/n Wireless LAN and Bluetooth Module |  |  |

| Major Chipset              | Infineon CYW43438 (WLBGA 63p)                       |  |  |

| Host Interface             | WLAN: SDIO v2.0<br>Bluetooth: UART                  |  |  |

| Dimension                  | 12.0mm(L) x 12.0mm(W) x 1.5 mm(H)                   |  |  |

| Form factor                | Stamp LGA Module, 47 pins                           |  |  |

| Antenna                    | 2.4G Ant: Wi-Fi/BT<br>FM Ant: FM                    |  |  |

| Weight                     | 0.4g                                                |  |  |

#### 1.3.2 WLAN

| Features           | Description                                                                                                                                                 |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLAN Standard      | IEEE 802.11 b/g/n, Wi-Fi compliant                                                                                                                          |

| WLAN VID/PID       | N/A                                                                                                                                                         |

| WLAN SVID/SPID     | N/A                                                                                                                                                         |

| Frequency Rage     | WLAN: 2.4 GHz                                                                                                                                               |

| Modulation         | DSSS, OFDM, BPSK(9/6Mbps), QPSK(18/12Mbps), DBPSK(1Mbps), DQPSK(2Mbps), CCK(11/5.5Mbps), 16-QAM(36/24Mbps), 64-QAM (72.2/54/48Mbps)                         |

| Number of Channels | 802.11b: USA, Canada and Taiwan - 1 ~ 11 Most European Countries - 1 ~ 13 Japan - 1 ~ 14  802.11g: USA and Canada - 1 ~ 11 Most European Countries - 1 ~ 13 |

|                      | 802.11n:                                                                                     |                          |                  |              |            |  |

|----------------------|----------------------------------------------------------------------------------------------|--------------------------|------------------|--------------|------------|--|

|                      | USA and Canada – 1 ~ 11                                                                      |                          |                  |              |            |  |

|                      | Most European Countries − 1 ~ 13                                                             |                          |                  |              |            |  |

|                      | 2.4G                                                                                         |                          |                  |              |            |  |

|                      |                                                                                              | Min                      | Тур              | Max          | Unit       |  |

| Output Power         | 11b (11Mbps)<br>@EVM<35%                                                                     | 16                       | 18               | 20           | dBm        |  |

|                      | 11g (54Mbps)<br>@EVM≦-25 dB                                                                  | 14                       | 16               | 18           | dBm        |  |

|                      | 11n (HT20 MCS7)<br>@EVM≦-27 dB                                                               | 13                       | 15               | 17           | dBm        |  |

|                      | 2.4G                                                                                         |                          |                  |              |            |  |

|                      |                                                                                              | Min                      | Тур              | Max          | Unit       |  |

|                      | 11b (1Mbps)                                                                                  |                          | -96              | -93          | dBm        |  |

| Receiver Sensitivity | 11g (6Mbps)                                                                                  |                          | -91              | -87          | dBm        |  |

|                      | 11b (11Mbps)                                                                                 |                          | -89              | -84          | dBm        |  |

|                      | 11g (54Mbps)                                                                                 |                          | -76              | -71          | dBm        |  |

|                      | 11n (HT20 MCS0)                                                                              |                          | -91              | -86          | dBm        |  |

|                      | 11n (HT20 MCS7)                                                                              |                          | -73              | -68          | dBm        |  |

|                      | 802.11b: 1, 2, 5.5, 11M                                                                      | bps                      |                  |              |            |  |

| Data Rate            | 802.11g: 6, 9, 12, 18, 2                                                                     |                          | 54Mbps           |              |            |  |

|                      | 802.11n:MCS 0~7 HT2                                                                          | .0                       |                  |              |            |  |

|                      | ♦ WPA™- and WPA2™                                                                            | <sup>и</sup> - (Personal | l) support for p | owerful encr | yption and |  |

|                      | authentication                                                                               |                          |                  |              |            |  |

|                      | AES and TKIP acceleration hardware for faster data encryption     and 803 11i compatibility. |                          |                  |              |            |  |

|                      | and 802.11i compatibility                                                                    |                          |                  |              |            |  |

| Security             | ◆ Cisco® Compatible Extension- (CCX, CCX 2.0, CCX 3.0, CCX 4.0, CCX5.0) certified            |                          |                  |              |            |  |

|                      |                                                                                              |                          |                  |              |            |  |

|                      | <ul><li>♦ Wi-Fi Protected Setup (WPS)</li><li>♦ WEP</li></ul>                                |                          |                  |              |            |  |

|                      | ♦ WMM / WMM-SA                                                                               |                          |                  |              |            |  |

|                      | ◆ CKIP(Software)                                                                             |                          |                  |              |            |  |

#### 1.3.3 Bluetooth

| Features           | Description                                                    |

|--------------------|----------------------------------------------------------------|

| Bluetooth Standard | Bluetooth 2.1+Enhanced Data Rate (EDR) /Core Specification 5.1 |

| Bluetooth VID/PID  | N/A                                                            |

| Frequency Rage     | 2400~2483.5MHz                                                 |

8

FORM NO.: FR2-015\_A Responsible Department: WBU Expiry Date: Forever The information contained herein is the exclusive property of AzureWave and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of AzureWave.

| Modulation           | GFSK (1Mbps), Π/4DQPSK (2Mbps) and 8DPSK (3Mbps) |     |     |     |      |

|----------------------|--------------------------------------------------|-----|-----|-----|------|

| Output Power         | 0≤ Output Power ≤ +10 dBm (Conductive)           |     |     |     |      |

|                      |                                                  | Min | Тур | Max | Unit |

| Receiver Sensitivity | DH5                                              |     | -91 | -82 | dBm  |

| Receiver Sensitivity | 2DH5                                             |     | -93 | -84 | dBm  |

|                      | 3DH5                                             |     | -87 | -78 | dBm  |

#### 1.3.4 Operating Conditions

| Features                    | Description                                                      |

|-----------------------------|------------------------------------------------------------------|

| Operating Conditions        |                                                                  |

| Voltage                     | WIFI/BT VBAT:3.2V~4.8V (3.6V Typical)                            |

| Operating Temperature       | -30°C to 85 °C (Optimal RF performance guarantee -20°C to 85 °C) |

| Operating Humidity          | less than 85% R.H.                                               |

| Storage Temperature         | -40°C to 85 °C                                                   |

| Storage Humidity            | less than 60% R.H.                                               |

| ESD Protection              |                                                                  |

| Human Body Model            | ±1.25KV per MIL-STD-883H Method 3015.8                           |

| <b>Charged Device Model</b> | ±175V per JEDEC EIA/JESD22-C101E                                 |

#### 2. Pin Definition

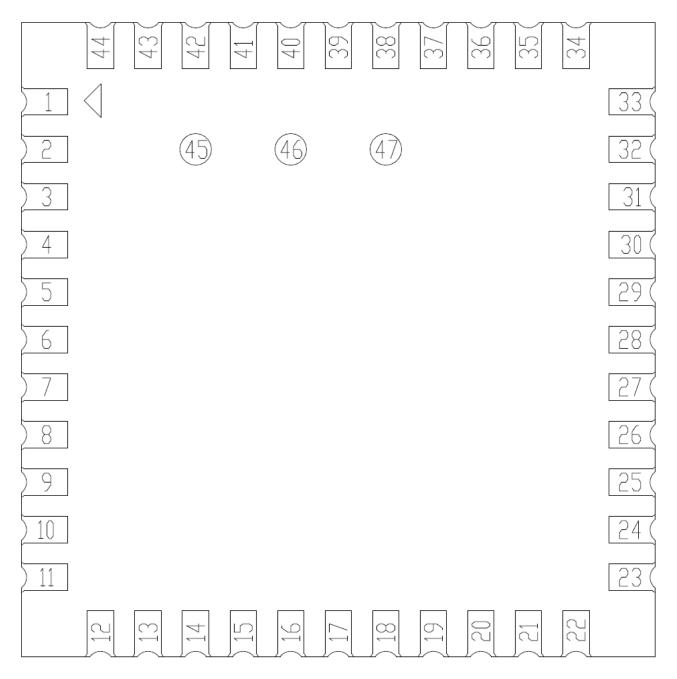

#### 2.1 Pin Map

AW-NM372SM Pin Map (Top View)

#### 2.2 Pin Table

| Pin No | Definition   | Basic Description                                                                                                                                                                                                                                                                 | Voltage | Туре     |

|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|

| 1      | GND          | Ground.                                                                                                                                                                                                                                                                           |         | GND      |

| 2      | WL_BT_ANT    | WLAN/BT RF TX/RX path.                                                                                                                                                                                                                                                            |         | RF       |

| 3      | GND          | Ground.                                                                                                                                                                                                                                                                           |         | GND      |

| 4      | FM_RX        | FM radio RF input.                                                                                                                                                                                                                                                                |         | RF       |

| 5      | NC           | Floating Pin, No connect to anything.                                                                                                                                                                                                                                             |         | Floating |

| 6      | BT_WAKE_DEV  | HOST wake-up Bluetooth device                                                                                                                                                                                                                                                     | VDDIO   | ı        |

| 7      | BT_HOST_WAKE | Bluetooth device to wake-up HOST                                                                                                                                                                                                                                                  | VDDIO   | 0        |

| 8      | CLK_REQ      | The module asserts CLK_REQ when Bluetooth or WLAN directs the host to turn on the reference clock. The CLK_REQ polarity is active-high                                                                                                                                            | VDDIO   | 0        |

| 9      | VBAT         | 3.3V power pin                                                                                                                                                                                                                                                                    | VBAT    | PWR      |

| 10     | NC           | Floating Pin, No connect to anything.                                                                                                                                                                                                                                             |         | Floating |

| 11     | NC           | Floating Pin, No connect to anything.                                                                                                                                                                                                                                             |         | Floating |

| 12     | WL_REG_ON    | Used by PMU to power up or power down the internal regulators used by the WLAN section. Also, when deasserted, this pin holds the WLAN section in reset. This pin has an internal 200k ohm pull down resistor that is enabled by default. It can be disabled through programming. | VDDIO   | I        |

| 13     | WL_HOST_WAKE | WLAN device to wake-up HOST                                                                                                                                                                                                                                                       | VDDIO   | 0        |

| 14     | SDIO_DATA_2  | SDIO Data Line 2                                                                                                                                                                                                                                                                  | VDDIO   | I/O      |

| 15     | SDIO_DATA_3  | SDIO Data Line 3                                                                                                                                                                                                                                                                  | VDDIO   | I/O      |

| 16     | SDIO_CMD     | SDIO Command Input                                                                                                                                                                                                                                                                | VDDIO   | I/O      |

| 17     | SDIO_CLK     | SDIO Clock Input                                                                                                                                                                                                                                                                  | VDDIO   | I        |

| 18     | SDIO_DATA_0  | SDIO Data Line 0                                                                                                                                                                                                                                                                  | VDDIO   | I/O      |

| 19     | SDIO_DATA_1  | SDIO Data Line 1                                                                                                                                                                                                                                                                  | VDDIO   | I/O      |

| 20     | GND          | Ground.                                                                                                                                                                                                                                                                           |         | GND      |

|    | 7120101101  | ecinologies, inc.                                                                                                                                                                                                                                                                           |          |          |

|----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|

| 21 | VIN_LDO_OUT | Internal Buck 1.2V voltage generation pin                                                                                                                                                                                                                                                   | 1.4V     | 0        |

| 22 | VDDIO       | 1.8V-3.3V VDDIO supply for WLAN and BT                                                                                                                                                                                                                                                      | VDDIO    | PWR      |

| 23 | VIN_LDO     | Internal Buck 1.2V voltage generation pin                                                                                                                                                                                                                                                   | 1.4V     | I        |

| 24 | LPO         | External 32K or RTC clock                                                                                                                                                                                                                                                                   | 0.2~3.3V | I        |

| 25 | PCM_OUT     | PCM data Out                                                                                                                                                                                                                                                                                | VDDIO    | 0        |

| 26 | PCM_CLK     | PCM Clock                                                                                                                                                                                                                                                                                   | VDDIO    | I/O      |

| 27 | PCM_IN      | PCM data Input                                                                                                                                                                                                                                                                              | VDDIO    | I        |

| 28 | PCM_SYNC    | PCM Synchronization control                                                                                                                                                                                                                                                                 | VDDIO    | 0        |

| 29 | NC          | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       |          | Floating |

| 30 | NC          | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       |          | Floating |

| 31 | GND         | Ground.                                                                                                                                                                                                                                                                                     |          | GND      |

| 32 | NC          | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       |          | Floating |

| 33 | GND         | Ground.                                                                                                                                                                                                                                                                                     |          | GND      |

| 34 | BT_REG_ON   | Used by PMU to power up or power down the internal regulators used by the Bluetooth section. Also, when deasserted, this pin holds the Bluetooth section in reset. This pin has an internal 200k ohm pull down resistor that is enabled by default. It can be disabled through programming. | VDDIO    | I        |

| 35 | NC          | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       |          | Floating |

| 36 | GND         | Ground.                                                                                                                                                                                                                                                                                     |          | GND      |

| 37 | NC          | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       |          | Floating |

| 38 | NC          | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       |          | Floating |

| 39 | GPIO2       | Wi-Fi Co-existence pin with LTE(WLAN_SECI_RX)                                                                                                                                                                                                                                               | VDDIO    | ı        |

| 40 | GPIO1       | Wi-Fi Co-existence pin with LTE(WLAN_SECI_TX)                                                                                                                                                                                                                                               | VDDIO    | 0        |

| 41 | UART_RTS_N  | High-Speed UART RTS                                                                                                                                                                                                                                                                         | VDDIO    | 0        |

| 42 | UART_OUT    | High-Speed UART Data Out                                                                                                                                                                                                                                                                    | VDDIO    | 0        |

| 43 | UART_IN     | High-Speed UART Data In                                                                                                                                                                                                                                                                     | VDDIO    | ı        |

| 44 | UART_CTS_N | High-Speed UART CTS                   | VDDIO | I        |

|----|------------|---------------------------------------|-------|----------|

| 45 | TP1        | FM Analog AUDIO left output.          |       | 0        |

| 46 | TP2        | FM Analog AUDIO right output          |       | 0        |

| 47 | TP3(NC)    | Floating Pin, No connect to anything. |       | Floating |

#### 3. Electrical Characteristics

#### 3.1 Absolute Maximum Ratings

| Symbol | Parameter                            | Minimum | Typical | Maximum | Unit |

|--------|--------------------------------------|---------|---------|---------|------|

| VBAT   | Power supply for Internal Regulators | -0.5    |         | 6       | V    |

| VDDIO  | DC supply voltage for digital I/O    | -0.5    |         | 3.9     | V    |

#### 3.2 Recommended Operating Conditions

| Symbol | Parameter                            | Minimum | Typical | Maximum | Unit |

|--------|--------------------------------------|---------|---------|---------|------|

| VBAT   | Power supply for Internal Regulators | 3*      | 3.6     | 4.8*    | ٧    |

<sup>\*</sup>Optimal RF performance is guaranteed only for 3.2V<VBAT<4.8V

#### 3.3 Digital IO Pin DC Characteristics

| Symbol    | Parameter                      | Minimum | Typical | Maximum | Unit |  |  |  |  |

|-----------|--------------------------------|---------|---------|---------|------|--|--|--|--|

| For SDIO  | For SDIO Interface VDDIO =1.8V |         |         |         |      |  |  |  |  |

| VIH       | Input high voltage             | 1.27    | -       | -       | V    |  |  |  |  |

| VIL       | Input low voltage              | -       | -       | 0.58    | V    |  |  |  |  |

| VOH       | Output High Voltage @ 2mA      | 1.4     | -       | -       | V    |  |  |  |  |

| VOL       | Output Low Voltage @ 2mA       | -       | -       | 0.45    | V    |  |  |  |  |

| For SDIO  | For SDIO Interface VDDIO =3.3V |         |         |         |      |  |  |  |  |

| VIH       | Input high voltage             | 2.06    | -       | -       | V    |  |  |  |  |

| VIL       | Input low voltage              | -       | -       | 0.82    | V    |  |  |  |  |

| VOH       | Output High Voltage @ 2mA      | 2.47    | -       | -       | V    |  |  |  |  |

| VOL       | Output Low Voltage @ 2mA       | -       | -       | 0.41    | V    |  |  |  |  |

| Other Dig | gital Interface VDDIO=1.8V     |         |         |         |      |  |  |  |  |

| VIH       | Input high voltage             | 1.17    | -       | -       | V    |  |  |  |  |

| VIL                           | Input low voltage                  | -    | - | 0.63 | V |  |

|-------------------------------|------------------------------------|------|---|------|---|--|

| VOH                           | Output High Voltage @ 2mA          | 1.35 | - | -    | V |  |

| VOL                           | Output Low Voltage @ 2mA           | -    | - | 0.45 | V |  |

| Other Di                      | Other Digital Interface VDDIO=3.3V |      |   |      |   |  |

| VIH                           | Input high voltage                 | 2    | - | -    | V |  |

| VIL                           | VIL Input low voltage              |      | - | 0.8  | V |  |

| VOH Output High Voltage @ 2mA |                                    | 2.9  | - | -    | V |  |

| VOL                           | VOL Output Low Voltage @ 2mA -     |      | - | 0.4  | V |  |

#### 3.4 Host Interface

#### 3.4.1 SDIO

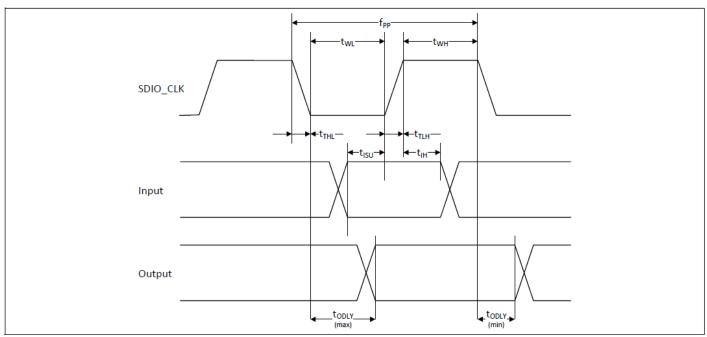

#### **SDIO Bus Timing (Default Mode)**

| Parameter                                                          | Symbol | Minimum | Typical | Maximum | Unit |  |  |  |

|--------------------------------------------------------------------|--------|---------|---------|---------|------|--|--|--|

| SDIO CLK (All values are referred to minimum VIH and maximum VIL*) |        |         |         |         |      |  |  |  |

| Frequency – Data Transfer mode                                     | fPP    | 0       | _       | 25      | MHz  |  |  |  |

| Frequency – Identification mode                                    | fOD    | 0       | _       | 400     | kHz  |  |  |  |

| Clock low time                                                     | tWL    | 10      | _       | _       | ns   |  |  |  |

| Clock high time                                                    | tWH    | 10      | _       | _       | ns   |  |  |  |

| Clock rise time                                                    | tTLH   | _       | _       | 10      | ns   |  |  |  |

| Clock low time                                                     | tTHL   | _       | _       | 10      | ns   |  |  |  |

| Inputs: CMD, DAT (referenced to CLK                                | )      |         |         |         |      |  |  |  |

| Input setup time                                                   | tISU   | 5       | _       |         | ns   |  |  |  |

| Input hold time                                                    | tIH    | 5       | _       |         | ns   |  |  |  |

| Outputs: CMD, DAT (referenced to CLK)                              |        |         |         |         |      |  |  |  |

| Output delay time – Data Transfer<br>mode | tODLY | 0 | 14 | ns |

|-------------------------------------------|-------|---|----|----|

| Output delay time – Identification mode   | tODLY | 0 | 50 | ns |

# **SDIO Bus Timing Parameters (Default Mode)**\* min (VIH) = 0.7 × VDDIO and max (VIL) = 0.2 × VDDIO

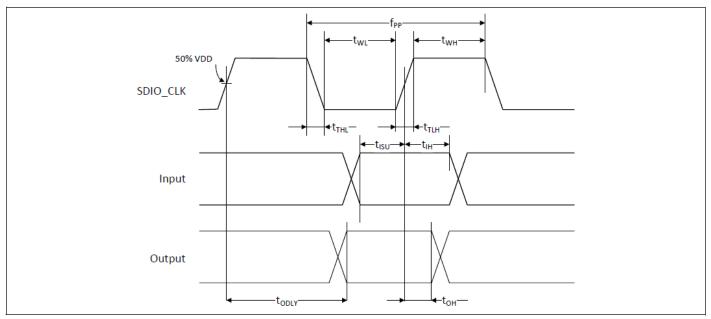

#### **SDIO Bus Timing (High-Speed Mode)**

| Parameter                                                          | Symbol | Minimum | Typical | Maximum | Unit |  |  |  |

|--------------------------------------------------------------------|--------|---------|---------|---------|------|--|--|--|

| SDIO CLK (all values are referred to minimum VIH and maximum VIL*) |        |         |         |         |      |  |  |  |

| Frequency – Data Transfer Mode                                     | fPP    | 0       | _       | 50      | MHz  |  |  |  |

| Frequency – Identification Mode                                    | fOD    | 0       | _       | 400     | kHz  |  |  |  |

| Clock low time                                                     | tWL    | 7       | _       | _       | ns   |  |  |  |

| Clock high time                                                    | tWH    | 7       | _       | _       | ns   |  |  |  |

| Clock rise time                                                    | tTLH   | _       | _       | 3       | ns   |  |  |  |

| Clock low time                                                     | tTHL   | _       | _       | 3       | ns   |  |  |  |

| Inputs: CMD, DAT (referenced to CLK)                               |        |         |         |         |      |  |  |  |

| Input setup Time                                                   | tISU   | 6       |         |         | ns   |  |  |  |

| Input hold Time                           | tIH   | 2   | _ | _  | ns |  |  |

|-------------------------------------------|-------|-----|---|----|----|--|--|

| Outputs: CMD, DAT (referenced to CLK)     |       |     |   |    |    |  |  |

| Output delay time – Data Transfer<br>Mode | tODLY |     | _ | 14 | ns |  |  |

| Output hold time                          | tOH   | 2.5 | _ | _  | ns |  |  |

| Total system capacitance (each line)      | CL    | _   | _ | 40 | pF |  |  |

**SDIO Bus Timing a Parameters (High-Speed Mode)**

#### 3.4.2 UART Interface

The AW-NM372SM includes a single UART for Bluetooth. The UART is a standard 4-wire interface (RX, TX, RTS, and CTS) with adjustable baud rates from 9600 bps to 4.0 Mbps. The interface features an automatic baud rate detection capability that returns a baud rate selection. Alternatively, the baud rate may be selected through a vendor-specific UART HCI command.

UART has a 1040-byte receive FIFO and a 1040-byte transmit FIFO to support EDR. Access to the FIFOs is conducted through the AHB interface through either DMA or the CPU. The UART supports the Bluetooth 5.1 UART HCI specification: H4, a custom Extended H4, and H5. The default baud rate is 115.2 Kbaud.

The UART supports the 3-wire H5 UART transport, as described in the Bluetooth specification ("Three-wire UART Transport Layer"). Compared to H4, the H5 UART transport reduces the number of signal lines required by eliminating the CTS and RTS signals.

The AW-NM372SM UART can perform XON/XOFF flow control and includes hardware support for the Serial Line Input Protocol (SLIP). It can also perform wake-on activity. For example, activity on the RX or CTS inputs can wake the chip from a sleep state.

Normally, the UART baud rate is set by a configuration record downloaded after device reset, or by automatic baud rate detection, and the host does not need to adjust the baud rate. Support for changing the baud rate during normal HCI UART operation is included through a vendor-specific command that allows the host to adjust the contents of the baud rate registers. The AW-NM372SM UARTs operate correctly with the host UART as long as the combined baud rate error of the two devices is within ±2%.

**UART Interface Signals**

| PIN No. Name Description Type |

|-------------------------------|

|-------------------------------|

18

FORM NO.: FR2-015\_A Responsible Department: WBU Expiry Date: Forever The information contained herein is the exclusive property of AzureWave and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of AzureWave.

<sup>\*</sup> min (VIH) =  $0.7 \times VDDIO$  and max (VIL) =  $0.2 \times VDDIO$

| 40 | UART_TXD   | Bluetooth UART Serial Output. Serial data output for the HCI UART Interface                      | 0 |

|----|------------|--------------------------------------------------------------------------------------------------|---|

| 41 | UART_RXD   | Bluetooth UART Series Input. Serial data input for the HCI UART Interface                        | I |

| 43 | UART_RTS_N | Bluetooth UART Request-to-Send. Active-low request-to-<br>send signal for the HCI UART interface | 0 |

| 42 | UART_CTS_N | Bluetooth UART Clear-to-Send. Active-low clear-to-send signal for the HCI UART interface.        | I |

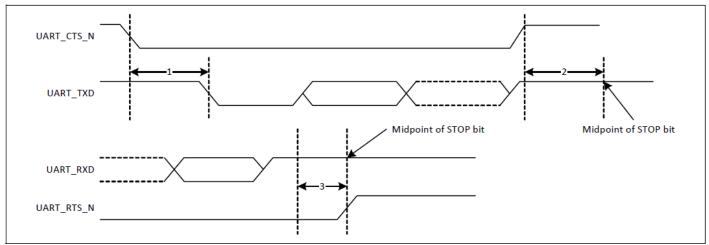

**UART Timing**

| Parameter | Reference Characteristics                               | Minimum | Typical | Maximum | Unit        |

|-----------|---------------------------------------------------------|---------|---------|---------|-------------|

|           | Delay time, UART_CTS_N low to UART_TXD valid            | -       | -       | 1.5     | Bit periods |

|           | Setup time, UART_CTS_N high before midpoint of stop bit | -       | -       | 0.5     | Bit periods |

|           | Delay time, midpoint of stop bit to UART_RTS_N high     | -       | -       | 0.5     | Bit periods |

**UART Timing Specifications**

#### 3.4.3 PCM Interface Timing

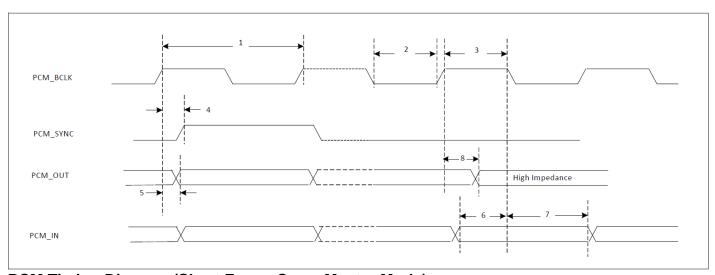

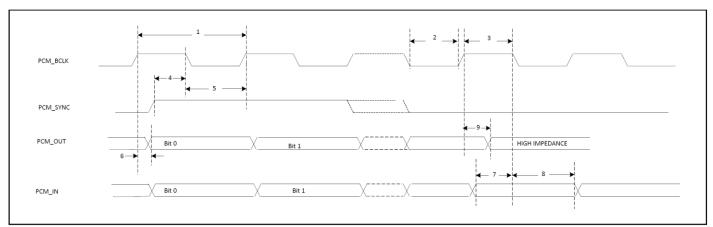

**PCM Timing Diagram (Short Frame Sync, Master Mode)**

| Parameter | Reference Characteristics                                                                    | Minimum | Typical | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      |         |         | 12      | MHz  |

| 2         | PCM bit clock low                                                                            | 41      |         |         | ns   |

| 3         | PCM bit clock high                                                                           | 41      |         |         | ns   |

| 4         | PCM_SYNC delay                                                                               | 0       |         | 25      | ns   |

| 5         | PCM_OUT delay                                                                                | 0       |         | 25      | ns   |

| 6         | PCM_IN setup                                                                                 | 8       |         |         | ns   |

| 7         | PCM_IN hold                                                                                  | 8       |         |         | ns   |

| 8         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       |         | 25      | ns   |

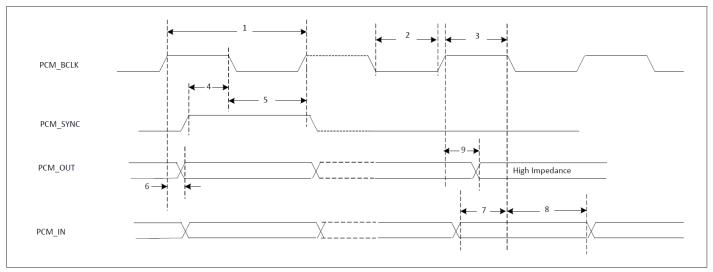

**PCM Timing Diagram (Short Frame Sync, Slave Mode)**

| Parameter | Reference Characteristics | Minimum | Typical | Maximum | Unit |

|-----------|---------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency   |         |         | 12      | MHz  |

| 2         | PCM bit clock low         | 41      |         |         | ns   |

| 3 | PCM bit clock high                                                                           | 41 |    | ns |

|---|----------------------------------------------------------------------------------------------|----|----|----|

| 4 | PCM_SYNC setup                                                                               | 8  |    | ns |

| 5 | PCM_SYNC hold                                                                                | 8  |    | ns |

| 6 | PCM_OUT delay                                                                                | 0  | 25 | ns |

| 7 | PCM_IN setup                                                                                 | 8  |    | ns |

| 8 | PCM_IN hold                                                                                  | 8  |    | ns |

| 9 | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0  | 25 | ns |

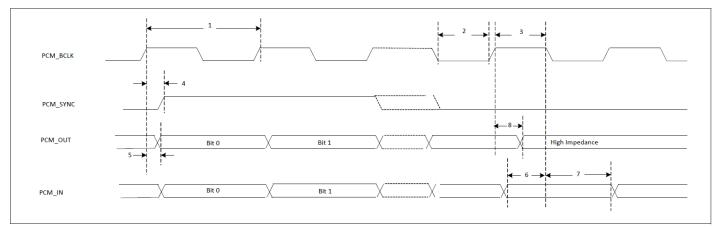

**PCM Timing Diagram (Long Frame Sync, Master Mode)**

| Parameter | Reference Characteristics | Minimum | Typical | Maximum | Unit |

|-----------|---------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency   |         |         | 12      | MHz  |

| 2         | PCM bit clock low         | 41      |         |         | ns   |

| 3         | PCM bit clock high        | 41      |         |         | ns   |

| 4         | PCM_SYNC delay            | 0       |         | 25      | ns   |

| 5         | PCM_OUT delay             | 0       |         | 25      | ns   |

| 6 | PCM_IN setup                                                                                 | 8 |    | ns |

|---|----------------------------------------------------------------------------------------------|---|----|----|

| 7 | PCM_IN hold                                                                                  | 8 |    | ns |

| 8 | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0 | 25 | ns |

**PCM Timing Diagram (Long Frame Sync, Slave Mode)**

| Parameter | Reference Characteristics                                                                             | Minimum | Typical | Maximum | Unit |

|-----------|-------------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                               |         |         | 12      | MHz  |

| 2         | PCM bit clock low                                                                                     | 41      |         |         | ns   |

| 3         | PCM bit clock high                                                                                    | 41      |         |         | ns   |

| 4         | PCM_SYNC setup                                                                                        | 8       |         |         | ns   |

| 5         | PCM_SYNC hold                                                                                         | 8       |         |         | ns   |

| 6         | PCM_OUT delay                                                                                         | 0       |         | 25      | ns   |

| 7         | PCM_IN setup                                                                                          | 8       |         |         | ns   |

| 8         | PCM_IN hold                                                                                           | 8       |         |         | ns   |

| 9         | Delay from rising edge of<br>PCM_BCLK during last bit period to<br>PCM_OUT becoming high<br>impedance | 0       |         | 25      | ns   |

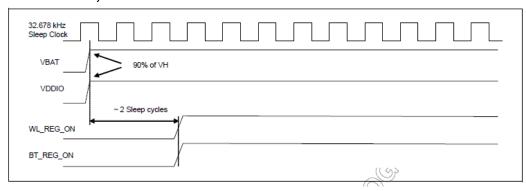

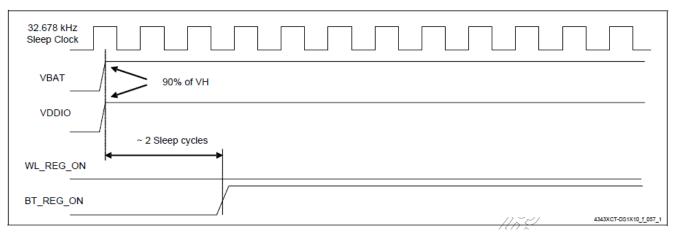

#### 3.5 Power up Timing Sequence

#### WLAN = ON, Bluetooth = ON

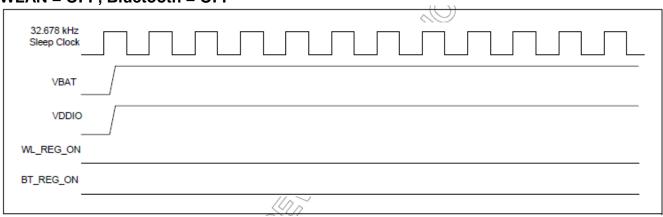

#### WLAN = OFF, Bluetooth = OFF

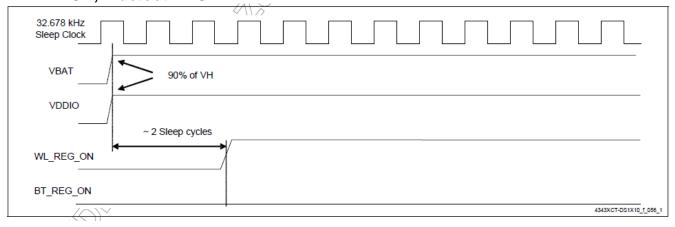

#### WLAN = ON, Bluetooth = OFF

WLAN = OFF, Bluetooth = ON

The information contained herein is the exclusive property of AzureWave and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of AzureWave.

#### 3.6 Frequency References

The AW-NM372SM uses an internal 26MHz xtal for normal operation and an external secondary low frequency clock for low-power-mode timing. Either the internal low-precision LPO or an external 32.768 kHz precision oscillator is required. The internal LPO frequency range is approximately 33 kHz ± 30% over process, voltage, and temperature, which is adequate for some applications. However, a trade-off caused by this wide LPO tolerance is a small current consumption increase during WLAN power save mode that is incurred by the need to wake up earlier to avoid missing beacons.

The preferred approach for WLAN is to connect a precision external 32.768 kHz clock that meets the requirements listed in Table below.

| Parameter                              | LPO                      | Units    |  |

|----------------------------------------|--------------------------|----------|--|

| Nominal input frequency                | 32.768                   | kHz      |  |

| Frequency accuracy                     | +-200                    | ppm      |  |

| Duty cycle                             | 30 - 70                  | %        |  |

| Input signal amplitude                 | 200 - 3300               | mV , p-p |  |

| Input impedance                        | >100                     | kΩ       |  |

| patpadaec                              | <5                       | pF       |  |

| Signal type                            | Square-wave or sine-wave | -        |  |

| Clock jitter (during initial start-up) | <10000                   | ррт      |  |

#### 3.7 Power Consumption\*

#### 3.7.1 WLAN

| Band    | Mode       | BW<br>(MHz) | RF<br>Power<br>(dBm) | Transmit |      |              | Receive |      |

|---------|------------|-------------|----------------------|----------|------|--------------|---------|------|

| (GHz)   |            |             |                      | Max.     | Avg. | Duty.<br>(%) | Max.    | Avg. |

| 2.4 (5) | 11b@1Mbps  | 20          | 17                   | 295      | 290  | 97.7         | 42      | 41   |

|         | 11b@11Mbps | 20          | 17                   | 248      | 247  | 80.4         | 42      | 41   |

|         | 11g@54Mbps | 20          | 15                   | 148      | 145  | 45.3         | 40      | 40   |

|         | 11n@MCS0   | 20          | 13                   | 223      | 222  | 86.5         | 42      | 41   |

|         | 11n@MCS7   | 20          | 13                   | 133      | 131  | 43.2         | 42      | 41   |

Current Unit: mA (5)Using MFG firmware.

#### 3.7.2 Bluetooth

| No. | Mode      | Packet Type | Power   | VBAT_IN=3.3 V |        |  |

|-----|-----------|-------------|---------|---------------|--------|--|

|     |           |             |         | Max.          | Avg.   |  |

| 1   | Deepsleep | N/A         | N/A     | 0.443         | 0.0056 |  |

| 2   | Transmit  | DH5         | 9 dBm   | 33.3          | 33.1   |  |

| 3   | Receive   | 3-DH5       | N/A     | 12.3          | 12.3   |  |

| 4   | Transmit  | LE          | 8.5 dBm | 31.2          | 31.1   |  |

| 5   | Receive   | LE          | N/A     | 13.2          | 13.2   |  |

<sup>\*</sup> The power consumption is based on Azurewave test environment, these data for reference only.

#### 4. Mechanical Information

#### 4.1 Mechanical Drawing

TOLERANCES UNLESS OTHERWISE SPECIFIED: ±0. Imm

Unit: mm

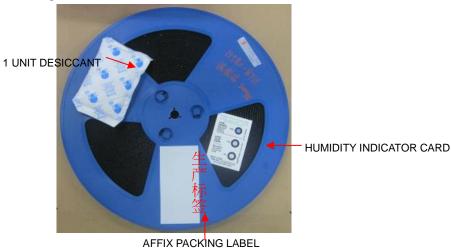

## 5. Packaging Information

#### 5.1

#### 5.2

#### 5.3

PINK BUBBLE WRAP

5.4

AFFIX PACKING LABEL

5.5

1 Carton= 5 Boxes

5.6