# AW-CB511NF-BPF

# IEEE 802.11 a/b/g/n/ac WLAN 2T2R with Bluetooth 5.1 Combo Module (M.2 2230)

# **Datasheet**

Rev. C

**B2**

(For Standard)

#### **Features**

#### **WLAN**

- ◆ IEEE 802.11ac Wave-2 compliant.

- Dual-stream spatial multiplexing up to 867 Mbps data rate.

- Supports 20, 40, and 80 MHz channels with optional SGI (256 QAM modulation).

- Full IEEE 802.11a/b/g/n legacy

compatibility with enhanced performance.

- TX and RX low-density parity check (LDPC) support for improved range and power efficiency.

- Supports IEEE 802.11ac/n beamforming.

- ♦ Supports RSDB.

- On-chip power amplifiers and low-noise amplifiers for both bands.

- Supports multipoint external coexistence interface to optimize bandwidth utilization with other co-located wireless technologies such as LTE and GPS.

- PCIe mode complies with PCI Express base specification

- Revision 3.0 for x1 lane and power management running at Gen1 speed.

- Worldwide regulatory support: Global products supported with worldwide homologated design.

- Integrated Arm® Cortex® -R4 processor with tightly coupled memory for complete

WLAN subsystem functionality, minimizing the need to wakeup the applications processor for standard WLAN functions. This allows for further minimization of power consumption, while maintaining the ability to field upgrade with future features.

With 2G and 5G internal Bandpass Filter.

#### Bluetooth

- Supports Bluetooth 5.1 optional features:

- Angel or Arrival (AoA)

- Angel of Departure (AoD)

- GATT Cache

- LE power control

- Supports all BT5.0 optional features including LE-2Mbps, LE-Long Range, LE-Advertising extensions.

- Bluetooth Class 1 or Class 2 transmitter operation.

- Supports extended synchronous connections (eSCO), for enhanced voice quality by allowing for retransmission of dropped packets.

- Adaptive frequency hopping (AFH) for reducing radio frequency interference.

- Interface support, host controller interface (HCI) using a high speed UART interface and PCM for audio data.

# **Bluetooth (continued)**

Supports multiple simultaneous

Advanced Audio Distribution Profiles

(A2DP) for stereo sound.

# **Revision History**

Document NO: R2-2511NF-DST-03

| Version | Revision<br>Date | DCN NO.   | Description                                                                               | Initials        | Approved        |

|---------|------------------|-----------|-------------------------------------------------------------------------------------------|-----------------|-----------------|

| Α       | 2022/12/19       | DCN028479 | Initial version                                                                           | Licheng<br>Wang | Chihhao<br>Liao |

| В       | 2023/05/16       | DCN029194 | <ul><li>Modify 3.4.2 UART description.</li><li>Update 5. Packaging Information.</li></ul> | Licheng<br>Wang | Chihhao<br>Liao |

| С       | 2024/10/30       | DCN032987 | Update 1.3.2 Number of channels.                                                          | Licheng<br>Wang | NC<br>Chen      |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           | -                                                                                         |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

|         |                  |           |                                                                                           |                 |                 |

# **Table of Contents**

| Revision History                                              | 4  |

|---------------------------------------------------------------|----|

| Table of Contents                                             | 5  |

| 1. Introduction                                               | 6  |

| 1.1 Product Overview                                          | 6  |

| 1.2 Block Diagram                                             | 7  |

| 1.2.1 Block Diagram                                           | 7  |

| 1.3 Specifications Table                                      | 8  |

| 1.3.1 General                                                 | 8  |

| 1.3.2 WLAN                                                    | 8  |

| 1.3.3 Bluetooth                                               | 10 |

| 1.3.4 Operating Conditions                                    | 11 |

| 2. Pin Definition                                             | 12 |

| 2.1 Pin Map                                                   | 12 |

| 2.2 Pin Table                                                 | 13 |

| 3. Electrical Characteristics                                 | 17 |

| 3.1 Absolute Maximum Ratings                                  | 17 |

| 3.2 Recommended Operating Conditions                          | 17 |

| 3.3 Digital IO Pin DC Characteristics                         |    |

| 3.3.1 PCIe Out-of-Band Signals (PERST0, PEWAKE0, and CLKREQ0) |    |

| 3.3.2 Other Digital I/O Pins                                  |    |

| 3.4 Power Up Timing Sequence                                  |    |

| 3.4.1 PCI Express (PCIe) Interface Specification              |    |

| 3.4.2 UART Interface                                          |    |

| 3.4.3 I2S Interface                                           |    |

| 3.4.4 PCM Interface                                           | _  |

| 3.5 Power Consumption                                         |    |

| 3.5.1 WLAN                                                    |    |

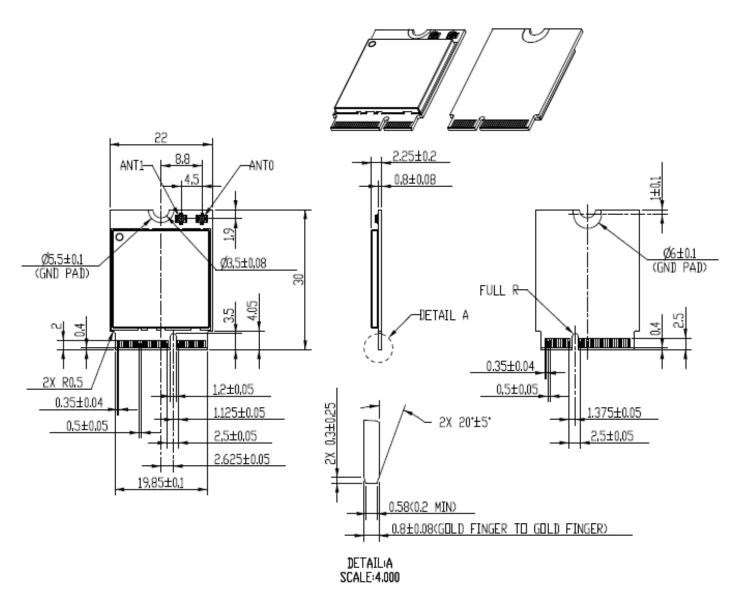

| 4. Mechanical Information                                     |    |

| 4.1 Mechanical Drawing                                        |    |

| 5. Packaging Information                                      | 37 |

#### 1. Introduction

#### 1.1 Product Overview

AzureWave Technologies, Inc. introduces the advanced IEEE 802.11 ac/a/b/g/n 2x2 MIMO WLAN and Bluetooth M.2 combo module - AW-CB511NF-BPF. The Module is a complete dual-band (2.4 GHz and 5 GHz) Wi-Fi 2x2 MIMO MAC/PHY/Radio system-on-module. This 5G Wi-Fi single-chip device provides a high level of integration with a dual-stream IEEE 802.11ac MAC/baseband/radio and Bluetooth 5.1. In IEEE 802.11ac mode, the WLAN operation supports rates of MCS0–MCS9 (up to 256 QAM) in 20 MHz, 40 MHz, and 80 MHz channels for data rates up to 867 Mbps. In addition, all the rates specified in IEEE 802.11a/b/g/n are supported. Included on-chip are the 2.4 GHz and 5 GHz transmit power amplifiers and receive low-noise amplifiers. The WLAN operation supports two fully simultaneous SISO channels and real simultaneous dual-band (RSDB).

For the WLAN section, the device interfaces to a host SoM processor through a PCIe v3.0-compliant interface running at Gen1 speed.

For the Bluetooth section, Host interface is through a high-speed 4-wire UART interface and PCM interface for audio.

In addition, the AW-CB511NF-BPF implements highly sophisticated enhanced collaborative coexistence hardware mechanisms and algorithms that ensure that WLAN and Bluetooth collaboration is optimized for maximum performance. Coexistence support for external radios (such as LTE cellular and GPS) is provided via an external interface. As a result, enhanced overall quality for simultaneous voice, video, and data transmission on a Commercial/Consumer systems is achieved.

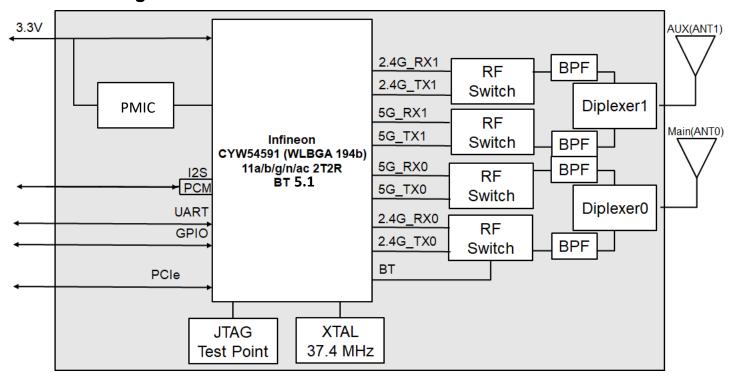

# 1.2 Block Diagram

### 1.2.1 Block Diagram

AW-CB511NF-BPF Block Diagram

# 1.3 Specifications Table

#### 1.3.1 General

| Features            | Description                                                                                       |

|---------------------|---------------------------------------------------------------------------------------------------|

| Product Description | IEEE 802.11 a/b/g/n/ac WLAN 2T2R with Bluetooth 5.1 Combo Module (M.2 2230)                       |

| Major Chipset       | Infineon CYW54591(wlbga 194b)                                                                     |

| Host Interface      | Wi-Fi: PCIe , BT: UART/PCM                                                                        |

| Dimension           | 22mm(L) 30xmm(W) x 2.25mm(H) (Typical)                                                            |

| Form factor         | M.2 2230 E Key                                                                                    |

| Antenna             | I-PEX MHF4 Connector Receptacle (20449) Ant 0(Main): Wi-Fi / BT → TX/RX Ant 1(Aux): Wi-Fi → TX/RX |

| Weight              | 2.55g                                                                                             |

#### 1.3.2 WLAN

| Features                                        | Description                                                                                                                                                                                                                                      |            |             |           |             |   |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-----------|-------------|---|

| WLAN Standard                                   | IEEE 802.11a/b/g/n/ac,                                                                                                                                                                                                                           | Wi-Fi comp | liant       |           |             |   |

| Frequency Rage                                  | 2.4 GHz ISM Bands 2.412-2.472 GHz 5.15-5.25 GHz (FCC UNII-low band) for US/Canada and Europe 5.25-5.35 GHz (FCC UNII-middle band) for US/Canada and Europe 5.47-5.725 GHz for Europe 5.725-5.825 GHz (FCC UNII-high band) for US/Canada          |            |             |           |             |   |

| Modulation                                      | 802.11a/g/n/ac: OFDM<br>802.11b: CCK(11, 5.5Mbps), DQPSK(2Mbps), BPSK(1Mbps)                                                                                                                                                                     |            |             |           |             |   |

| Number of<br>Channels                           | 2.4GHz ■ USA, NORTH AMERICA, Canada and Taiwan – 1 ~ 13¹ ■ China, Australia, Most European Countries – 1 ~ 13 5GHz  USA, EUROPE – 36, 40, 44, 48, 52, 56, 60, 64, 100, 104, 108, 112, 116, 120, 124, 128, 132, 136, 140, 149, 153, 157, 161, 165 |            |             |           |             |   |

| Output Power <sup>23</sup> (Board Level Limit)* | 2.4G<br>11b (11Mbps)                                                                                                                                                                                                                             | Min<br>15  | Тур<br>17.5 | Max<br>20 | Unit<br>dBm | ] |

<sup>&</sup>lt;sup>1</sup> Due to certification in different countries, the power limits for different frequency bands may vary.

<sup>&</sup>lt;sup>2</sup> EVM Spec are under typical test conditions.

<sup>&</sup>lt;sup>3</sup> Output Power means measurement power inside the range (Min and Max) with spectral mask and EVM compliance.

| p. of restrictive constitution of the second | AEVM 050/                                              | T       | T T    |       |      |   |

|----------------------------------------------|--------------------------------------------------------|---------|--------|-------|------|---|

|                                              | @EVM<35%                                               |         |        |       |      |   |

|                                              | 11g (54Mbps)                                           | 15      | 17.5   | 20    | dBm  |   |

|                                              | @EVM≦-25 dB                                            | 17.0 20 |        | aBiii |      |   |

|                                              | 11n (HT20 MCS7)                                        | 445     | 4.7    | 40.5  | -ID  |   |

|                                              | @EVM≦-27 dB                                            | 14.5    | 17     | 19.5  | dBm  |   |

|                                              | 5G                                                     |         |        |       |      |   |

|                                              |                                                        | Min     | Тур    | Max   | Unit |   |

|                                              | 11a (54Mbps)                                           |         |        |       |      |   |

|                                              | @EVM≦-25 dB                                            | 11.5    | 14     | 16.5  | dBm  |   |

|                                              | 11n (HT20 MCS7)                                        |         |        |       |      |   |

|                                              | @EVM≦-27 dB                                            | 11.5    | 14     | 16.5  | dBm  |   |

|                                              | 11n (HT40 MCS7)                                        | 40.5    | 40     | 45.5  | ID   |   |

|                                              | @EVM≦-27 dB                                            | 10.5    | 13     | 15.5  | dBm  |   |

|                                              | 11ac (VHT20 MCS8)                                      | 40.5    | 40 455 | 45.5  | -ID  |   |

|                                              | @EVM≦-30 dB                                            | 10.5    | 13     | 15.5  | dBm  |   |

|                                              | 11ac (VHT40 MCS9)                                      | 40.5    | 40     | 45.5  | ID   |   |

|                                              | @EVM≦-32 dB                                            | 10.5    | 13     | 15.5  | dBm  |   |

|                                              | 11ac (VHT80 MCS9)                                      | 0       | 44 5   | 1.1   | dD.m |   |

|                                              | @EVM≦-32 dB                                            | 9       | 11.5   | 14    | dBm  |   |

|                                              | 2.4G                                                   |         |        |       |      |   |

|                                              |                                                        | Min     | Тур    | Max   | Unit |   |

|                                              | 11b (11Mbps)                                           |         | -89    | -86   | dBm  |   |

|                                              | 11g (54Mbps)                                           |         | -76    | -73   | dBm  |   |

|                                              | 11n (HT20 MCS7)                                        |         | -75    | -72   | dBm  |   |

| Receiver Sensitivity                         | 5G                                                     |         |        |       |      | j |

| Receiver Sensitivity                         |                                                        | Min     | Тур    | Max   | Unit |   |

|                                              | 11a (54Mbps)                                           |         | -74.5  | -71.5 | dBm  |   |

|                                              | 11n (HT20 MCS7)                                        |         | -73    | -70   | dBm  |   |

|                                              | 11n (HT40 MCS7)                                        |         | -70    | -67   | dBm  |   |

|                                              | 11ac <sup>4</sup> (VHT20 MCS8)                         |         | -68    | -65   | dBm  |   |

|                                              | 11ac <sup>5</sup> (VHT40 MCS9)                         |         | -62    | -59   | dBm  |   |

|                                              | 11ac <sup>6</sup> (VHT80 MCS9)                         |         | -60    | -57   | dBm  |   |

|                                              | WLAN:                                                  |         |        |       |      |   |

| Data Rate                                    | 802.11b : 1, 2, 5.5, 11M                               | •       |        |       |      |   |

| Data Nato                                    | 802.11a/g: 6, 9, 12, 18,                               |         | •      | •     | _    |   |

|                                              | 802.11ac/n : Maximum data rates up to 192.6 Mbps(20MHz |         |        |       |      |   |

<sup>&</sup>lt;sup>4</sup> Tested by BCC instead of LDPC.

<sup>&</sup>lt;sup>5</sup> Tested by BCC instead of LDPC.

<sup>&</sup>lt;sup>6</sup> Tested by BCC instead of LDPC.

|          | channel),400 Mbps (40 MHz channel), 866.7 Mbps (80 MHz channel)                                                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security | <ul> <li>WPA, WAPI STA, and WPA2 (Personal) support for powerful encryption and authentication.</li> <li>AES and TKIP in hardware for faster data encryption and IEEE 802.11i compatibility.</li> </ul> |

|          | <ul> <li>Reference WLAN subsystem provides Wi-Fi Protected Setup (WPS).</li> </ul>                                                                                                                      |

<sup>\*</sup> If you have any certification questions about output power please contact FAE directly.

### 1.3.3 Bluetooth

| Features                 | Description                                       |             |       |       |      |  |

|--------------------------|---------------------------------------------------|-------------|-------|-------|------|--|

| Bluetooth Standard       | BT5.1+Enhanced Da                                 | ata Rate (E | DR)   |       |      |  |

| Bluetooth VID/PID        | N/A                                               |             |       |       |      |  |

| Frequency Rage           | 2402MHz~2483MHz                                   |             |       |       |      |  |

| Modulation               | Header GFSK Payload 2M: 4-DQPSK Payload 3M: 8DPSK |             |       |       |      |  |

|                          |                                                   | Min         | Тур   | Max   | Unit |  |

| Output Power             | BR                                                | 7.5         | 10    | 12.5  | dBm  |  |

| Output I Owel            | BLE(1M)                                           | 7.5         | 10    | 12.5  | dBm  |  |

|                          | BLE(2M)                                           | 6.5         | 9     | 11.5  | dBm  |  |

|                          |                                                   |             |       |       |      |  |

|                          |                                                   | Min         | Тур   | Max   | Unit |  |

| Receiver                 | BR                                                |             | -91   | -88   | dBm  |  |

|                          | EDR(π/4-DQPSK)                                    |             | -94   | -91   | dBm  |  |

| Sensitivity <sup>7</sup> | EDR(8DPSK)                                        |             | -88.5 | -85.5 | dBm  |  |

|                          | BLE(1M)                                           |             | -99   | -96   | dBm  |  |

|                          | BLE(2M)                                           |             | -96   | -93   | dBm  |  |

<sup>&</sup>lt;sup>7</sup> Tested by sLNA.

# 1.3.4 Operating Conditions

| Operating Conditions        | Operating Conditions           |  |  |  |

|-----------------------------|--------------------------------|--|--|--|

| Voltage                     | Power supply for host:3.3V     |  |  |  |

| Operating Temperature       | -40°C to +85°C <sup>8</sup>    |  |  |  |

| Operating Humidity          | less than 85% R.H.             |  |  |  |

| Storage Temperature         | -40°C to +85°C                 |  |  |  |

| Storage Humidity            | less than 60% R.H.             |  |  |  |

| ESD Protection              |                                |  |  |  |

| Human Body Model            | 2KV per JEDEC EID/JESD22-A114  |  |  |  |

| <b>Changed Device Model</b> | 300V per JEDEC EIA/JESD22-C101 |  |  |  |

$<sup>^{8}~\</sup>text{-}40^{\circ}\text{C}^{\sim}85^{\circ}\text{C}~$  is Functional operation, for detail please check with AzureWave FAE.

# 2. Pin Definition

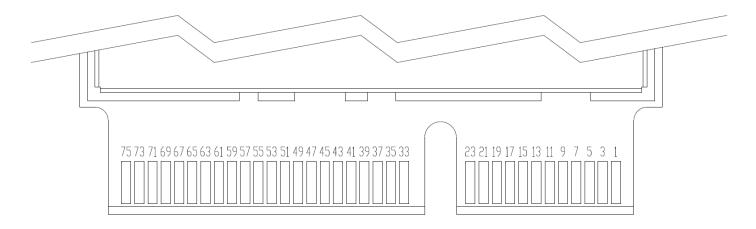

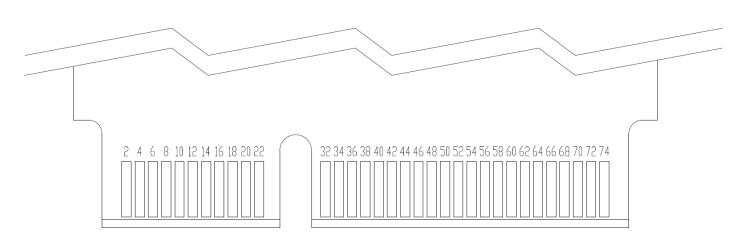

# 2.1 Pin Map

AW-CB511NF-BPF Pin Map (Top View)

**AW-CB511NF-BPF Pin Map (Bottom View)**

# 2.2 Pin Table

| Pin No | Definition         | Basic Description                                                                                       | Voltage | Туре |

|--------|--------------------|---------------------------------------------------------------------------------------------------------|---------|------|

| 1      | GND                | System Ground Pin                                                                                       |         |      |

| 2      | 3.3V               | 3.3V Power Supply                                                                                       | 3.3V    | I    |

| 3      | NC                 | NC                                                                                                      |         |      |

| 4      | 3.3V               | 3.3V Power supply input                                                                                 | 3.3V    | I    |

| 5      | NC                 | NC                                                                                                      |         |      |

| 6      | NC                 | NC                                                                                                      |         |      |

| 7      | GND                | System Ground Pin                                                                                       |         |      |

| 8      | PCM_CLK/I2S_SCK    | PCM clock; can be master (output) or slave (input). I2S clock, can be master (output) or slave (input). | 1.8V    | I/O  |

| 9      | NC                 | NC                                                                                                      |         |      |

| 10     | PCM_SYNC/I2S_WS    | PCM sync; can be master (output) or slave (input). I2S WS; can be master (output) or slave (input).     | 1.8V    | I/O  |

| 11     | NC                 | NC                                                                                                      |         |      |

| 12     | PCM_OUT/I2S_SD_OUT | PCM data output. I2S data output.                                                                       | 1.8V    | 0    |

| 13     | NC                 | NC                                                                                                      |         |      |

| 14     | PCM_IN/I2S_SD_IN   | PCM data input.<br>I2S data input.                                                                      | 1.8V    | 1    |

| 15     | NC                 | NC                                                                                                      |         |      |

| 16     | NC                 | NC                                                                                                      |         |      |

| 17     | NC                 | NC                                                                                                      |         |      |

| 18     | GND                | System Ground Pin                                                                                       |         |      |

| 19     | NC                 | NC                                                                                                      |         |      |

| 20     | BT_HOST_WAKE       | Bluetooth HOST_WAKE                                                                                     | 3.3V    | I/O  |

| 21     | NC                 | NC                                                                                                      |         |      |

| 22     | BT_UART_TXD        | UART serial output. Serial data output for the HCI UART interface.                                      | 1.8V    | 0    |

| 23     | NC                 | NC                                                                                                      |         | _    |

in whole or in part without prior written permission of AzureWave.

| NC                       | NC                                                                                                                                                                                |                                          |                                          |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------|

| NC                       | NC                                                                                                                                                                                |                                          |                                          |

| BT_UART_RXD              | UART serial input. Serial data input for the HCI UART interface.                                                                                                                  | 1.8V                                     | I                                        |

| GND                      | System Ground Pin                                                                                                                                                                 |                                          |                                          |

| BT_UART_RTS              | UART request-to-send. Active-low request-to-send signal for the HCI UART interface. BT LED control pin.                                                                           | 1.8V                                     | 0                                        |

| PERp0                    | PCIe receiver differential pair (×1 lane).                                                                                                                                        | 3.3V                                     | I                                        |

| BT_UART_CTS              | UART clear-to-send. Active-low clear-to-send signal for the HCI UART interface.                                                                                                   | 1.8V                                     | I                                        |

| PERn0                    | PCIe receiver differential pair (×1 lane).                                                                                                                                        | 3.3V                                     | I                                        |

| NC                       | NC                                                                                                                                                                                |                                          |                                          |

| GND                      | System Ground Pin                                                                                                                                                                 |                                          |                                          |

| CLK_REQ                  | Reference clock request (shared by BT and WLAN). If not used, this can be no-connect.                                                                                             | 1.8V                                     | 0                                        |

| РЕТр0                    | PCIe transmitter differential pair (×1 lane).                                                                                                                                     | 3.3V                                     | 0                                        |

| BT_DEV_WAKE              | Bluetooth DEV_WAKE.                                                                                                                                                               | 1.8V                                     | I/O                                      |

| PETn0                    | PCIe transmitter differential pair (×1 lane).                                                                                                                                     | 3.3V                                     | 0                                        |

| NC                       | NC                                                                                                                                                                                |                                          |                                          |

| GND                      | System Ground Pin                                                                                                                                                                 |                                          |                                          |

| GPIO9_WL_UART_TX<br>_1V8 | GPIO.                                                                                                                                                                             | 1.8V                                     | I/O                                      |

| REFCLKp0                 | PCIe differential Clock inputs (negative and positive). 100 MHz differential                                                                                                      | 3.3V                                     | I                                        |

| GPIO8_WL_UART_RX<br>_1V8 | GPIO.                                                                                                                                                                             | 1.8V                                     | I/O                                      |

| REFCLKn0                 | PCIe differential Clock inputs (negative and positive). 100 MHz differential                                                                                                      | 3.3V                                     | I                                        |

|                          | NC NC NC NC NC NC NC NC NC ST_UART_RXD GND ST_UART_RTS PERP0 BT_UART_CTS PERn0 NC GND CLK_REQ PETp0 BT_DEV_WAKE PETn0 NC GND GPIO9_WL_UART_TX _1V8 REFCLKp0 GPIO8_WL_UART_RX _1V8 | NC N | NC N |

14

FORM NO.: FR2-015\_ A

The information contained herein is the exclus

Responsible Department: WBU

**Expiry Date: Forever**

The information contained herein is the exclusive property of AzureWave and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of AzureWave.

| 50 | EXT_LPO    | External sleep clock input (32.768 kHz).                                                                                                                                                                                                                                                                                    | 3.3V | I  |

|----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|

| 51 | GND        | System Ground Pin                                                                                                                                                                                                                                                                                                           |      |    |

| 52 | PERST0     | PCIe System Reset. This input is the PCIe reset as defined in the PCIe base specification v1.1. PERST0 pad excludes internal pull-up.                                                                                                                                                                                       | 3.3V | I  |

| 53 | CLKREQ0    | PCIe clock request signal which indicates when the REFCLK to the PCIe interface can be gated.  1 = the clock can be gated.  0 = the clock is required.                                                                                                                                                                      | 3.3V | OD |

| 54 | W_DISABLE2 | BT_REG_ON; Used by PMU to power up or power down the internal AW-CB511NF-BPF regulators used by the Bluetooth section. Also, when deasserted, this pin holds the Bluetooth section in reset. This pin has an internal 200 k $\Omega$ pull-down resistor that is enabled by default. It can be disabled through programming. | 3.3V | ı  |

| 55 | PEWAKE0    | PCI power management event output. Used to request a change in the device or system power state. The assertion and deassertion of this signal is asynchronous to the PCIe reference clock. This signal has an open-drain output structure, as per the PCI Bus Local Bus Specification, revision 2.3.                        | 3.3V | OD |

| 56 | W_DISABLE1 | WL_REG_ON; Used by PMU to power up or power down the internal AW-CB511NF-BPF regulators used by the WLAN section. Also, when deasserted, this pin holds the WLAN section in reset. This pin has an internal 200 kΩ pull-down resistor that is enabled by default. It can be disabled through programming.                   | 3.3V | ı  |

| 57 | GND        | System Ground Pin                                                                                                                                                                                                                                                                                                           |      |    |

| 58 | NC         | NC                                                                                                                                                                                                                                                                                                                          |      |    |

| 59 | NC         | NC                                                                                                                                                                                                                                                                                                                          |      |    |

| 60 | NC         | NC                                                                                                                                                                                                                                                                                                                          |      |    |

| 61 | NC         | NC                                                                                                                                                                                                                                                                                                                          |      |    |

| 62 | NC         | NC                                                                                                                                                                                                                                                                                                                          |      |    |

| 63 | GND        | System Ground Pin                                                                                                                                                                                                                                                                                                           |      |    |

| 64 | NC         | NC                                                                                                                                                                                                                                                                                                                          |      |    |

| 65 | NC         | NC                                                                                                                                                                                                                                                                                                                          |      |    |

| 66 | NC         | NC                                                                                                                                                                                                                                                                                                                          |      |    |

| 67 | NC   | NC                |      |   |

|----|------|-------------------|------|---|

| 68 | NC   | NC                |      |   |

| 69 | GND  | System Ground Pin |      |   |

| 70 | NC   | NC                |      |   |

| 71 | NC   | NC                |      |   |

| 72 | 3.3V | 3.3V Power Supply | 3.3V | I |

| 73 | NC   | NC                |      |   |

| 74 | 3.3V | 3.3V Power Supply | 3.3V | I |

| 75 | GND  | System Ground Pin |      |   |

### 3. Electrical Characteristics

# 3.1 Absolute Maximum Ratings

| Symbol | Parameter                             | Minimum | Typical | Maximum | Unit |

|--------|---------------------------------------|---------|---------|---------|------|

| 3.3V   | DC supply voltage for VBAT and VDDIO. | -0.5    | -       | +3.9    | V    |

# 3.2 Recommended Operating Conditions

| Symbol | Parameter                             | Minimum        | Typical | Maximum | Unit |

|--------|---------------------------------------|----------------|---------|---------|------|

| VBAT   | DC supply voltage for VBAT and VDDIO. | 3 <sup>9</sup> | 3.3     | 3.6     | V    |

# 3.3 Digital IO Pin DC Characteristics

# 3.3.1 PCle Out-of-Band Signals (PERST0, PEWAKE0, and CLKREQ0)

| Symbol Parameter                                       |                                         | Minimum       | Typical | Maximum       | Unit |  |  |  |  |

|--------------------------------------------------------|-----------------------------------------|---------------|---------|---------------|------|--|--|--|--|

| VDDIO=1.8V                                             |                                         |               |         |               |      |  |  |  |  |

| ViH                                                    | Input high voltage (V <sub>DDIO</sub> ) | 1.27          | -       | 3.63          | V    |  |  |  |  |

| VIL                                                    | Input low voltage (VDDIO)               | -             | -       | 0.58          | V    |  |  |  |  |

| VoL                                                    | Output Low Voltage @ 2mA                | -             |         |               | V    |  |  |  |  |

| VDDIO=3                                                | .3V                                     |               |         |               |      |  |  |  |  |

| V <sub>IH</sub>                                        | Input high voltage (VDDIO)              | 0.625 × VDDIO | -       | 3.63          | V    |  |  |  |  |

| V <sub>IL</sub> Input low voltage (V <sub>DDIO</sub> ) |                                         | -             | -       | 0.25 × VDDIO  | V    |  |  |  |  |

| VoL Output Low Voltage @ 2mA                           |                                         | -             | -       | 0.125 × VDDIO | V    |  |  |  |  |

in whole or in part without prior written permission of AzureWave.

<sup>&</sup>lt;sup>9</sup> AW-CB511NF-BPF is functional across this range of voltages. Optimal RF performance specified in the data sheet, however, is guaranteed only for 3.2V < VBAT < 3.6V.

# 3.3.2 Other Digital I/O Pins

| Symbol Parameter                                        |                                         | Minimum      | Typical | Maximum      | Unit |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------|--------------|---------|--------------|------|--|--|--|--|

| VDDIO=1.8V                                              |                                         |              |         |              |      |  |  |  |  |

| V <sub>IH</sub> Input high voltage (V <sub>DDIO</sub> ) |                                         | 0.65 × VDDIO | -       | 3.63         | V    |  |  |  |  |

| VıL                                                     | Input low voltage (VDDIO)               | -            | -       | 0.35 × VDDIO | V    |  |  |  |  |

| Vон                                                     | Output High Voltage @ 2mA               | VDDIO – 0.45 | -       | -            | V    |  |  |  |  |

| VoL                                                     | Output Low Voltage @ 2mA                | -            | -       | 0.45         | V    |  |  |  |  |

| VDDIO=3                                                 | 3.3V                                    |              |         |              |      |  |  |  |  |

| V <sub>IH</sub>                                         | Input high voltage (V <sub>DDIO</sub> ) | 2.0          | -       | 3.63         | V    |  |  |  |  |

| VIL                                                     | Input low voltage (VDDIO)               | -            | -       | 0.8          | V    |  |  |  |  |

| Voh                                                     | Output High Voltage @ 2mA               | VDDIO – 0.4  | -       | -            | V    |  |  |  |  |

| VoL                                                     | Output Low Voltage @ 2mA                | -            | -       | 0.4          | V    |  |  |  |  |

in whole or in part without prior written permission of AzureWave.

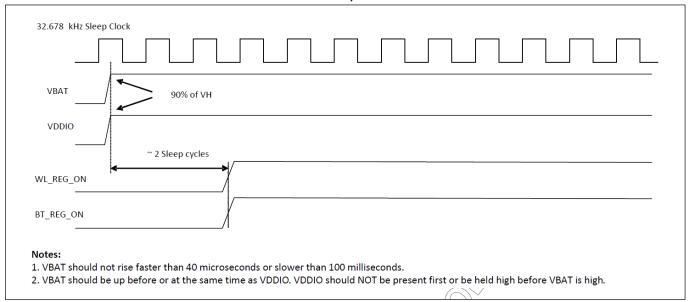

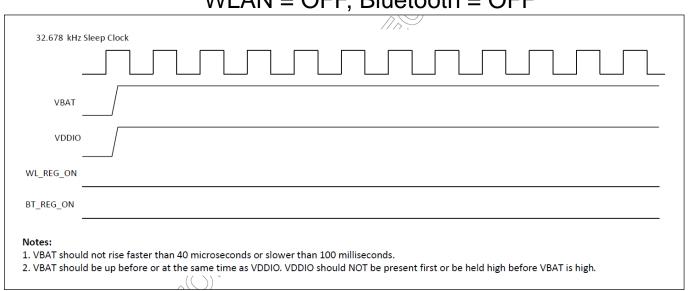

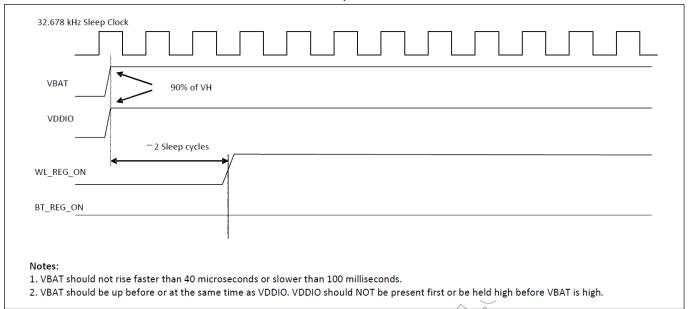

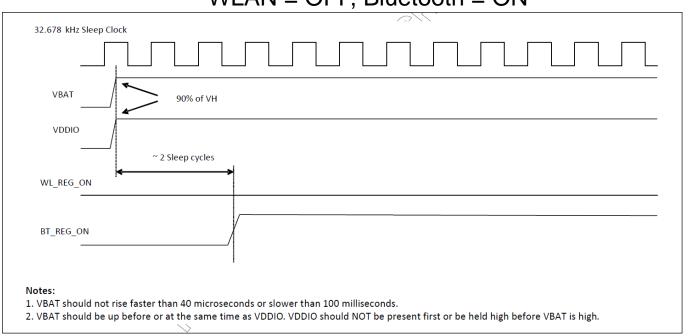

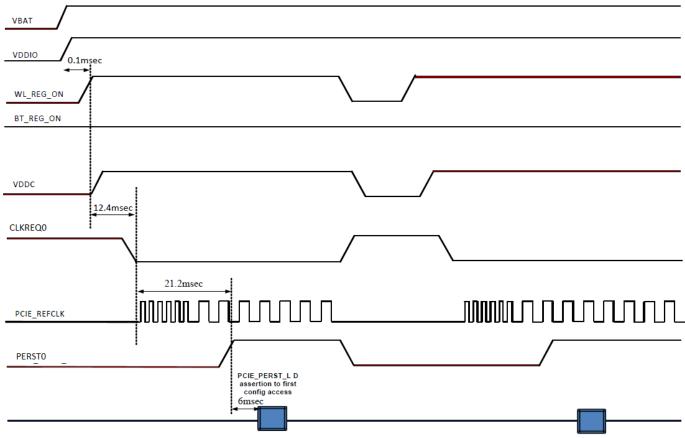

### 3.4 Power Up Timing Sequence

The AW-CB511NF-BPF has two signals that allow the host to control power consumption by enabling or disabling the Bluetooth, WLAN, and internal regulator blocks. These signals are described below. Additionally, diagrams are provided to indicate proper sequencing of the signals for various operational states. The timing values indicated are minimum required values; longer delays are also acceptable.

Description of Control Signals (Power-Up/Power-Down/Reset Control Signals)

| Signal                    | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W_DISABLE1<br>(WL_REG_ON) | Used by the PMU to power up the WLAN section. It is also OR-gated with the W_DISABLE2(BT_REG_ON) input to control the internal AW-CB511NF-BPF regulators. When this pin is high, the regulators are enabled and the WLAN section is out of reset. When this pin is low the WLAN section is in reset. If both the W_DISABLE2(BT_REG_ON) and W_DISABLE1(WL_REG_ON) pins are low, the regulators are disabled. |

|                           | Used by the PMU (OR-gated with W_DISABLE1) to power up the internal AW-CB511NF-BPF regulators. If both the W_DISABLE2(BT_REG_ON) and W_DISABLE1(WL_REG_ON) pins are low, the regulators are disabled. When this pin is low and W_DISABLE1(WL_REG_ON), the BT section is in reset.                                                                                                                           |

#### **Control Signal Timing Diagrams**

# WLAN = ON, Bluetooth = ON

# WLAN = OFF, Bluetooth = OFF

# WLAN = ON, Bluetooth = OFF

# WLAN = OFF, Bluetooth = ON

# WLAN Power-Up Sequence for PCIe Host

There is variation of about +/-30% on above timing numbers

# 3.4.1 PCI Express (PCIe) Interface Specification

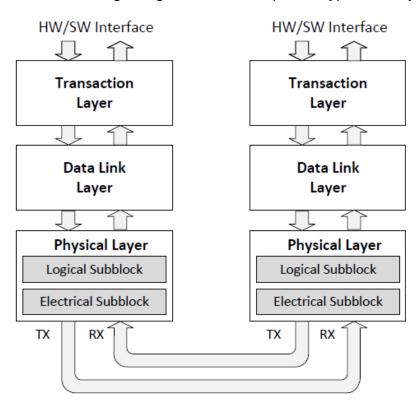

The PCI Express core on the AW-CB511NF-BPF is a high-performance serial I/O interconnect that is protocol compliant and electrically compatible with the PCI Express Base Specification v3.0 running at Gen1 speeds. This core contains all the necessary blocks, including logical and electrical functional subblocks to perform PCIe functionality and maintain high-speed links, using existing PCI system configuration software implementations without modification.

Organization of the PCIe core is in logical layers: Transaction Layer, Data Link Layer, and Physical Layer, as shown in below figure. A configuration or link management block is provided for enumerating the PCIe configuration space and supporting generation and reception of System Management Messages by communicating with PCIe layers.

Each layer is partitioned into dedicated transmit and receive units that allow point-to-point communication between the host and AW-CB511device. The transmit side processes outbound packets whereas the receive side processes inbound packets. Packets are formed and generated in the Transaction and Data Link Layer for transmission onto the high-speed links and onto the receiving device. A header is added at the beginning to indicate the packet type and any other optional fields.

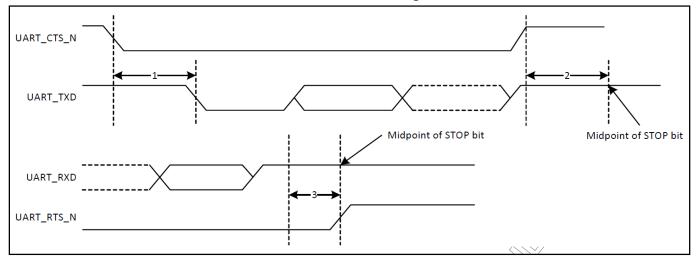

#### 3.4.2 UART Interface

The AW-CB511NF-BPF UART is a standard 4-wire interface (RX, TX, RTS, and CTS) with adjustable baud rates from 9600 bps to 4.0 Mbps. The interface features an automatic baud rate detection capability that returns a baud rate selection. Alternatively, the baud rate may be selected through a vendor-specific UART HCI command.

UART has a 1040-byte receive FIFO and a 1040-byte transmit FIFO to support EDR. Access to the FIFOs is conducted through the AHB interface through either DMA/CPU. The UART supports the Bluetooth 5.1 UART HCI specification: H4, and H5. The default baud rate is 115.2 Kbaud.

The CYW54591 UART can perform XON/XOFF flow control and includes hardware support for the Serial Line Input Protocol (SLIP). It can also perform wake-on activity. For example, activity on the RX or CTS inputs can wake the chip from a sleep state.

Normally, the UART baud rate is set by a configuration record downloaded after device reset, or by automatic baud rate detection, and the host does not need to adjust the baud rate. Support for changing the baud rate during normal HCI UART operation is included through a vendor-specific command that allows the host to adjust the contents of the baud rate registers. The AW-CB511NF-BPF UARTs operate correctly with the host UART as long as the combined baud rate error of the two devices is within ±2%.UART Interface Signals

| PIN No. | Name          | Description                                                                                      | Туре |

|---------|---------------|--------------------------------------------------------------------------------------------------|------|

| 22      |               | Bluetooth UART Serial Output. Serial data output for the HCI UART Interface                      | 0    |

| 32      | BT_UART_RXD   | Bluetooth UART Series Input. Serial data input for the HCI UART Interface                        | I    |

| 34      |               | Bluetooth UART Request-to-Send. Active-low request-to-<br>send signal for the HCI UART interface | 0    |

| 36      | BT_UART_CTS_N | Bluetooth UART Clear-to-Send. Active-low clear-to-send signal for the HCI UART interface.        | I    |

# **Example of Common Baud Rates**

| Desired Rate | Actual Rate | Error (%) |

|--------------|-------------|-----------|

| 400000       | 400000      | 0.00      |

| 3692000      | 3692308     | 0.01      |

| 3000000      | 3000000     | 0.00      |

| 2000000      | 2000000     | 0.00      |

| 1500000      | 1500000     | 0.00      |

| 1444444      | 1454544     | 0.70      |

| 921600       | 923077      | 0.16      |

| 460800       | 461538      | 0.16      |

| 230400       | 230796      | 0.17      |

| 115200       | 115385      | 0.16      |

| 57600        | 57692       | 0.16      |

| 38400        | 38400       | 0.00      |

| 28800        | 28846       | 0.16      |

| 19200        | 19200       | 0.00      |

| 14400        | 14423       | 0.16      |

| 9600         | 9600        | 0.00      |

# **UART Timing**

# **UART Timing Specifications**

| Ref No. | Characteristics A                                       | Minimum     | Typical | Maximum | Unit        |

|---------|---------------------------------------------------------|-------------|---------|---------|-------------|

| 1       | Delay time, UART_CTS_N low to UART_TXD valid -          | - 8         | _       | 1.5     | Bit periods |

| 2       | Setup time, UART_CTS_N high before midpoint of stop bit |             | -       | 0.5     | Bit periods |

| 3       | Delay time, midpoint of stop bit to UART_RTS_N - high   | <u>&gt;</u> | _       | 0.5     | Bit periods |

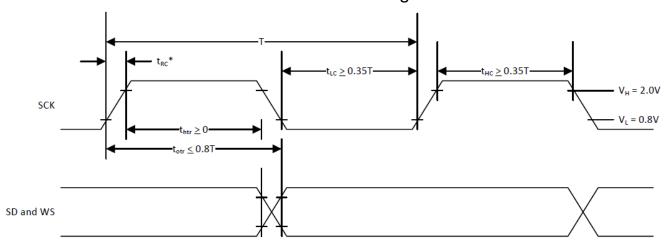

#### 3.4.3 I2S Interface

The AW-CB511NF-BPF supports I2S digital audio port for Bluetooth audio which shared the pin out with PCM interface.

The I2S signals are:

■ I2S clock: I2S\_SCK

■ I2S Word Select: I2S\_WS

■ I2S Data Out: I2S\_SD\_OUT

■ I2S Data In: I2S\_SD\_IN

I2S\_SCK and I2S\_WS become outputs in Master mode and inputs in Slave mode, whereas BT\_I2S\_DO always stays as an output. The channel word length is 16 bits, and the data is justified so that the MSb of the left-channel data is aligned with the MSb of the I2S bus, in accord with the I2S specification. The MSb of each data word is transmitted one bit clock cycle after the I2S\_WS transition, synchronous with the falling edge of the bit clock. Left-channel data is transmitted when I2S\_WS is LOW, and right channel data is transmitted when I2S\_WS is HIGH. Data bits sent by the AW-CB511NF-BPF are synchronized with the falling edge of I2S\_SCK and should be sampled by the receiver on the rising edge of I2S\_SCK.

The clock rate in master mode is either of the following:

48 kHz x 32 bits per frame = 1.536 MHz

48 kHz × 50 bits per frame = 2.400 MHz

The master clock is generated from the input reference clock using a N/M clock divider.

In the slave mode, any clock rate is supported to a maximum of 3.072 MHz.

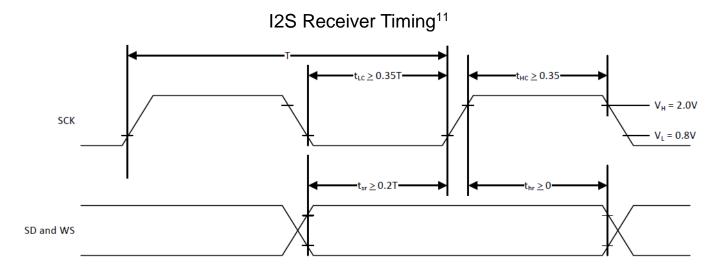

# **I2S Timing**

|                              |                     | Trans               | mitter              |                  |                     | Rece                | eiver |             |    |

|------------------------------|---------------------|---------------------|---------------------|------------------|---------------------|---------------------|-------|-------------|----|

|                              | Lower Limit         |                     | Upper               | pper Limit Lower |                     | r Limit             | Upper | Upper Limit |    |

|                              | Min                 | Max                 | Min                 | Max              | Min                 | Max                 | Min   | Max         |    |

| Clock Period T               | T <sub>tr</sub>     | _                   | -                   | _                | T <sub>r</sub>      | -                   | _     | -           | 7  |

| Master Mode: Clock generated | d by transn         | nitter or re        | ceiver              |                  |                     |                     |       |             |    |

| HIGH t <sub>HC</sub>         | 0.35T <sub>tr</sub> | _                   | _                   | -                | 0.35T <sub>tr</sub> | _                   | -     | _           | 8  |

| LOWt <sub>LC</sub>           | 0.35T <sub>tr</sub> | _                   | _                   | _                | 0.35T <sub>tr</sub> | _                   | -     | _           | 8  |

| Slave Mode: Clock accepted b | y transmit          | ter or rece         | iver                |                  | •                   |                     | 1     | -           | 1  |

| HIGH t <sub>HC</sub>         | _                   | 0.35T <sub>tr</sub> | -                   | _                | _                   | 0.35T <sub>tr</sub> | -     | -           | 9  |

| LOW t <sub>LC</sub>          | _                   | 0.35T <sub>tr</sub> | -                   | -                | _                   | 0.35T <sub>tr</sub> | -     | -           | 9  |

| Rise time t <sub>RC</sub>    | _                   | _                   | 0.15T <sub>tr</sub> | _                | _                   | -                   |       | -           | 10 |

| Transmitter                  | 1                   | 1                   |                     |                  | '                   |                     |       |             | 1  |

| Delay t <sub>dtr</sub>       | _                   | _                   | _                   | 0.8T             | _                   | _                   | _     | _           | 11 |

| Hold time t <sub>htr</sub>   | 0                   | _                   | -                   | -                | _                   | -                   | _     | _           | 10 |

| Receiver                     |                     |                     |                     |                  |                     |                     |       |             |    |

| Setup time t <sub>sr</sub>   | _                   | _                   | _                   | _                | _                   | 0.2T <sub>r</sub>   | _     | _           | 12 |

| Hold time t <sub>hr</sub>    | _                   | _                   | -                   | _                | _                   | 0                   | _     | -           | 12 |

#### Notes

- The system clock period T must be greater than T<sub>tr</sub> and T<sub>r</sub> because both the transmitter and receiver have to be able to handle the data transfer rate.

- At all data rates in master mode, the transmitter or receiver generates a clock signal with a fixed mark/space ratio. For this reason, t<sub>HC</sub> and t<sub>LC</sub> are specified with

- In slave mode, the transmitter and receiver need a clock signal with minimum HIGH and LOW periods so that they can detect the signal. So long as the minimum periods are greater than  $0.35T_{\rm p}$ , any clock that meets the requirements can be used.

- 10. Because the delay (t<sub>dtr</sub>) and the maximum transmitter speed (defined by T<sub>tr</sub>) are related, a fast transmitter driven by a slow clock edge can result in t<sub>dtr</sub> not exceeding t<sub>RC</sub> which means t<sub>htr</sub> becomes zero or negative. Therefore, the transmitter has to guarantee that t<sub>htr</sub> is greater than or equal to zero, so long as the clock rise-time t<sub>RC</sub> is not more than t<sub>RCmax</sub>, where t<sub>RCmax</sub> is not less than 0.15T<sub>tr</sub>.

11. To allow data to be clocked out on a falling edge, the delay is specified with respect to the rising edge of the clock signal and T, always giving the receiver sufficient

- 12. The data setup and hold time must not be less than the specified receiver setup and hold time.

**Expiry Date: Forever**

# I2S Transmitter Timing<sup>10</sup>

T = Clock period

T<sub>tr</sub> = Minimum allowed clock period for transmitter

$T = T_t$

<sup>\*</sup> t<sub>RC</sub> is only relevant for transmitters in slave mode.

T = Clock period

T<sub>r</sub> = Minimum allowed clock period for transmitter

T > T,

<sup>&</sup>lt;sup>10</sup> The time periods specified in I2C transmitter timing and I2C receiver timing are defined by the transmitter speed. The receiver specifications must match transmitter performance.

<sup>&</sup>lt;sup>11</sup> The time periods specified in I2C transmitter timing and I2C receiver timing are defined by the transmitter speed. The receiver specifications must match transmitter performance.

#### 3.4.4 PCM Interface

The AW-CB511 supports independent PCM interfaces that share the pins with the I2S interfaces. The PCM Interface on the AW-CB511NF-BPF can connect to linear PCM codec devices in Master/Slave mode. In Master mode, the AW-CB511NF-BPF generates the BT\_PCM\_CLK and BT\_PCM\_SYNC signals, and in Slave mode, these signals are provided by another master on the PCM interface and are inputs to the AW-CB511NF-BPF.

The configuration of the PCM interface may be adjusted by the host through the use of vendorspecific HCI commands.

#### 3.4.4.1 Slot Mapping

The AW-CB511NF-BPF supports up to three simultaneous full-duplex SCO or eSCO channels through the PCM interface. These three channels are time-multiplexed onto the single PCM interface by using a time-slotting scheme where the 8 kHz or 16 kHz audio sample interval is divided into as many as 16 slots. The number of slots is dependent on the selected interface rate of 128 kHz, 512 kHz, or 1024 kHz. The corresponding number of slots for these interface rate is 1, 2, 4, 8, and 16, respectively. Transmit and receive PCM data from a SCO channel is always mapped to the same slot. The PCM data output driver tristates its output on unused slots to allow other devices to share the same PCM interface signals. The data output driver tristates its output after the falling edge of the PCM clock during the last bit of the slot.

#### 3.4.4.2 Frame Synchronization

The AW-CB511NF-BPF supports both short and long-frame synchronization in both master and slave modes. In short-frame synchronization mode, the frame synchronization signal is an active-high pulse at the audio frame rate that is a single-bit period in width and is synchronized to the rising edge of the bit clock. The PCM slave looks for a high on the falling edge of the bit clock and expects the first bit of the first slot to start at the next rising edge of the clock. In long-frame synchronization mode, the frame synchronization signal is again an active-high pulse at the audio frame rate; however, the duration is three bit periods and the pulse starts coincident with the first bit of the first slot.

#### 3.4.4.3 Data Formatting

The AW-CB511NF-BPF may be configured to generate and accept several different data formats. For conventional narrowband speech mode, the AW-CB511NF-BPF uses 13 of the 16 bits in each PCM frame. The location and order of these 13 bits can be configured to support various data formats on the PCM interface. The remaining three bits are ignored on the input and may be filled with 0s, 1s, a sign bit, or a programmed value on the output. The default format is 13-bit 2's complement data, left justified, and clocked Most Significant Bit (MSb) first.

#### 3.4.4.4 Wideband Speech Support

When the host encodes WBS packets in transparent mode, the encoded packets are transferred over the PCM bus for an eSCO voice connection. In this mode, the PCM bus is typically configured in master mode for a 4 kHz sync rate with 16-bit samples, resulting in a 64 Kbps bit rate. The AW-CB511NF-BPF also supports slave transparent mode using a proprietary rate-matching scheme. In SBCcode mode, linear 16-bit data at 16 kHz (256 Kbps rate) is transferred over the PCM bus.

#### 3.4.4.5 PCM Interface Timing

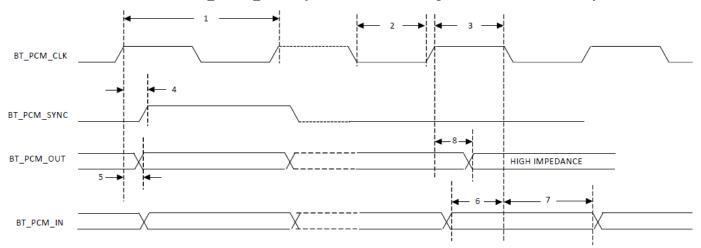

Short Frame Sync, Master Mode

# **PCM Timing Diagram (Short Frame Sync, Master Mode)**

# **PCM Interface Timing Specifications (Short Frame Sync, Master Mode)**

|           | <u> </u>                                                                                           |      | •   |      | ,    |

|-----------|----------------------------------------------------------------------------------------------------|------|-----|------|------|

| Reference | Characteristics                                                                                    | Min  | Тур | Max  | Unit |

| 1         | PCM bit clock frequency                                                                            | _    | _   | 12.0 | MHz  |

| 2         | PCM bit clock LOW                                                                                  | 41.0 | -   | _    | ns   |

| 3         | PCM bit clock HIGH                                                                                 | 41.0 | _   | _    | ns   |

| 4         | BT_PCM_SYNC delay                                                                                  | 0    | -   | 25.0 | ns   |

| 5         | BT_PCM_OUT delay                                                                                   | 0    | -   | 25.0 | ns   |

| 6         | BT_PCM_IN setup                                                                                    | 8.0  | -   | _    | ns   |

| 7         | BT_PCM_IN hold                                                                                     | 8.0  | -   | _    | ns   |

| 8         | Delay from rising edge of BT_PCM_CLK during last bit period to BT_PCM_OUT becoming high impedance. | 0    | -   | 25.0 | ns   |

|           |                                                                                                    |      |     |      |      |

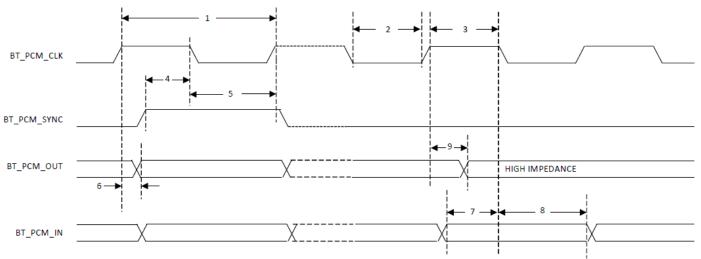

Short Frame Sync, Slave Mode

# **PCM Timing Diagram (Short Frame Sync, Slave Mode)**

# **PCM Interface Timing Specifications (Short Frame Sync, Slave Mode)**

| Reference | Characteristics                                                                                    | Min  | Тур | Max  | Unit |

|-----------|----------------------------------------------------------------------------------------------------|------|-----|------|------|

| 1         | PCM bit clock frequency                                                                            | _    | _   | 12.0 | MHz  |

| 2         | PCM bit clock LOW                                                                                  | 41.0 | _   | _    | ns   |

| 3         | PCM bit clock HIGH                                                                                 | 41.0 | _   | -    | ns   |

| 4         | BT_PCM_SYNC setup                                                                                  | 8.0  | _   | -    | ns   |

| 5         | BT_PCM_SYNC hold                                                                                   | 8.0  | -   | -    | ns   |

| 6         | BT_PCM_OUT delay                                                                                   | 0    | _   | 25.0 | ns   |

| 7         | BT_PCM_IN setup                                                                                    | 8.0  | _   | -    | ns   |

| 8         | BT_PCM_IN hold                                                                                     | 8.0  | -   | -    | ns   |

| 9         | Delay from rising edge of BT_PCM_CLK during last bit period to BT_PCM_OUT becoming high impedance. | 0    | _   | 25.0 | ns   |

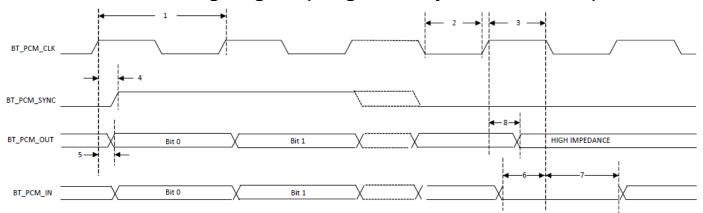

Long Frame Sync, Master Mode

# **PCM Timing Diagram (Long Frame Sync, Master Mode)**

## **PCM Interface Timing Specifications (Long Frame Sync, Master Mode)**

|           | 5 1                                                                                                | ,    | ,   |      | ,    |

|-----------|----------------------------------------------------------------------------------------------------|------|-----|------|------|

| Reference | Characteristics                                                                                    | Min  | Тур | Max  | Unit |

| 1         | PCM bit clock frequency                                                                            | -    | -   | 12.0 | MHz  |

| 2         | PCM bit clock LOW                                                                                  | 41.0 | _   | _    | ns   |

| 3         | PCM bit clock HIGH                                                                                 | 41.0 | -   | _    | ns   |

| 4         | BT_PCM_SYNC delay                                                                                  | 0    | -   | 25.0 | ns   |

| 5         | BT_PCM_OUT delay                                                                                   | 0    | -   | 25.0 | ns   |

| 6         | BT_PCM_IN setup                                                                                    | 8.0  | -   | _    | ns   |

| 7         | BT_PCM_IN hold                                                                                     | 8.0  | _   | _    | ns   |

| 8         | Delay from rising edge of BT_PCM_CLK during last bit period to BT_PCM_OUT becoming high impedance. | 0    | -   | 25.0 | ns   |

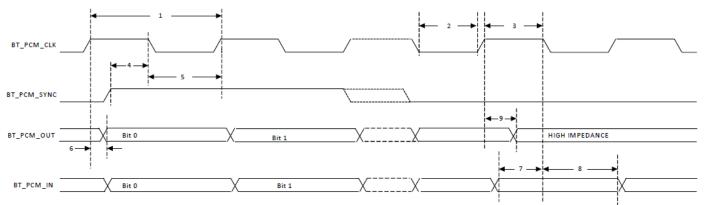

Long Frame Sync, Slave Mode

# **PCM Timing Diagram (Long Frame Sync, Slave Mode)**

# PCM Interface Timing Specifications (Long Frame Sync, Slave Mode)

| r om mondo rinning opositioanone (20119 i raino oyilo, ciavo modo) |                                                                                                    |      |     |       |      |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|-----|-------|------|

| Reference                                                          | Characteristics                                                                                    | Min  | Тур | Max   | Unit |

| 1                                                                  | PCM bit clock frequency                                                                            | _    | _   | 12.0  | MHz  |

| 2                                                                  | PCM bit clock LOW                                                                                  | 41.0 | _   | _     | ns   |

| 3                                                                  | PCM bit clock HIGH                                                                                 | 41.0 | -   | _     | ns   |

| 4                                                                  | BT_PCM_SYNC setup                                                                                  | 8.0  | _   | _     | ns   |

| 5                                                                  | BT_PCM_SYNC hold                                                                                   | 8.0  | _   | _     | ns   |

| 6                                                                  | BT_PCM_OUT delay                                                                                   | 0    | -   | 25.0. | ns   |

| 7                                                                  | BT_PCM_IN setup                                                                                    | 8.0  | _   | _     | ns   |

| 8                                                                  | BT_PCM_IN hold                                                                                     | 8.0. | _   | _     | ns   |

| 9                                                                  | Delay from rising edge of BT_PCM_CLK during last bit period to BT_PCM_OUT becoming high impedance. | 0    | -   | 25.0  | ns   |

# 3.5 Power Consumption<sup>12</sup>

#### 3.5.1 WLAN

|               | Mode           | BW<br>(MHz) | RF Power<br>(dBm) | Transmit |      |           | Receive |      |

|---------------|----------------|-------------|-------------------|----------|------|-----------|---------|------|

| Band<br>(GHz) |                |             |                   | Max.     | Avg. | Duty<br>% | Max.    | Avg. |

| 2.4           | 11b@1M         | 20          | 17.5              | 391      | 382  | 98        | 129     | 121  |

|               | 11g@54M        | 20          | 17.5              | 301      | 299  | 64        | -       | -    |

|               | 11n@MCS7       | 20          | 17.5              | 299      | 296  | 62        | 124     | 124  |

|               | 11n@MCS15      | 20          | 17.5              | 427      | 426  | 53        | -       | -    |

| 5             | 11a@6Mbps      | 20          | 14                | 431      | 427  | 93        | -       | -    |

|               | 11n@MCS8       | 40          | 13                | 673      | 670  | 78        | -       | -    |

|               | 11n@MCS15      | 40          | 13                | 456      | 454  | 43        | -       | -    |

|               | 11ac@MSC8 NSS1 | 20          | 12.5              | 315      | 313  | 61        | -       | -    |

|               | 11ac@MSC8 NSS2 | 20          | 12.5              | 436      | 435  | 51        | -       | -    |

|               | 11ac@MSC0 NSS2 | 40          | 12.5              | 657      | 653  | 78        | -       | -    |

|               | 11ac@MSC9 NSS1 | 40          | 12.5              | 316      | 315  | 47        | 236     | 231  |

|               | 11ac@MSC9 NSS2 | 40          | 12.5              | 438      | 436  | 42        | -       | -    |

|               | 11ac@MSC0 NSS2 | 80          | 11.5              | 658      | 656  | 67        | -       | -    |

<sup>&</sup>lt;sup>12</sup> For Details, please contact Azurewave FAE

# 3.6 Frequency Reference

The AW-CB511NF-BPF requires an external low-frequency clock for low-power mode timing. An external 32.768 kHz precision oscillator which meets the requirements listed in below table must be used.

| Parameter                             | LPO Clock                | Unit    |

|---------------------------------------|--------------------------|---------|

| Nominal input frequency               | 32.768                   | kHz     |

| Frequency accuracy                    | ±250                     | ppm     |

| Duty cycle                            | 30-70                    | %       |

| Input signal amplitude                | 200–3300                 | m∨, p-p |

| Signal type                           | Square-wave or sine-wave | -       |

| Input impedance <sup>[5]</sup>        | > 100k                   | Ω       |

| imput impedance · ·                   | < 5                      | pF      |

| Clock jitter (during initial startup) | < 10,000                 | ppm     |

Note

<sup>5.</sup> When power is applied or switched off.

### 4. Mechanical Information

# 4.1 Mechanical Drawing

TOLERANCE UNLESS OTHERWISE SPECIFIED: ± 0.15mm

# 5. Packaging Information

1. 84pcs M.2 2230 modules put in one tray

2. The trays are stacked with each other, and add more one tray on the top, so the total number of trays is 14pcs, i.e. 13pcs tray (full) and 1pcs tray (empty)

in whole or in part without prior written permission of AzureWave.

3. Use P.P Strap to pack 14pcs trays and add one packing label on the top

Example:

4. Put the two packed tray into the box

5. Seal the carton by AzureWave tape

6. One carton label and one box label pasted on the carton. If the carton is not full, add one balance label pasted on the carton

#### **Label Information on the carton**

| Example of carton label  | 6                                                  | AzureWave                  |  |  |  |

|--------------------------|----------------------------------------------------|----------------------------|--|--|--|

|                          | AzureWave P/N                                      | AW-XXXXX                   |  |  |  |

|                          | Customer                                           | customer Provided by Sales |  |  |  |

|                          | Customer P/N                                       | Provided by Sales          |  |  |  |

|                          | Customer P/O                                       | Provided by Sales          |  |  |  |

|                          | Description AW-XXXXX                               |                            |  |  |  |

|                          | Q'ty                                               | 依照实际出货数量<br>依实际情况填写        |  |  |  |

|                          | C/N                                                |                            |  |  |  |

|                          | N.W.                                               | G.W.                       |  |  |  |

|                          | RoHS Made in China                                 |                            |  |  |  |

| Example of box label     | 2-XXXXX-XXX<br>数量: XXX<br>BOX0275351 XXXXXX 股份有限公司 |                            |  |  |  |

| Example of balance label | В                                                  | 尾 数<br>Balance             |  |  |  |