## AW-NM432SM

# IEEE 802.11 b/g/n Wireless LAN Stamp Module

## **Datasheet**

Rev. A

DF

(For Standard)

#### **Features**

#### **WLAN**

- Integrates Cypress solutions of CYW43364

WiFi SoC

- SDIO v2.0 interfaces support for WLAN

- Lead-free Design

- 12.0mm(L) x 12.0mm(W) x 1.5 mm(H) 47 pin

LGA package

- With Crystal(XTAL)

- Single band 2.4 GHz 802.11 b/g/n

- WLAN host interface options

- SDIO v2.0, including DS and HS modes

- Security-WEP, WPA/WPA2 (personal), AES (HW), TKIP (HW), CKIP (SW), WMM/WMM-PS/WMM-SA

## **Revision History**

Document NO: R2-2432SM-DST-01

| Version     | Revision<br>Date | DCN NO.   | Descriptio                                  | n     | Initials      | Approved        |

|-------------|------------------|-----------|---------------------------------------------|-------|---------------|-----------------|

| Version 0.1 | 2019/02/15       |           | Initial Version                             |       | Sonia<br>Yang | Chihhao<br>Liao |

| Version 0.2 | 2019/05/06       |           | <ul><li>Specifications<br/>update</li></ul> | Table | JM.Pang       | Chihhao<br>Liao |

| Α           | 2019/11/21       | DCN016358 | Format Update                               |       | JM.Pang       | Chihhao<br>Liao |

|             |                  |           |                                             | . (   |               |                 |

|             |                  |           |                                             | * 6   | 9             |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  |           | 0,                                          |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  | 10        |                                             |       |               |                 |

|             |                  | M         |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             | , r              |           |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

|             |                  |           |                                             |       |               |                 |

#### **Table of Contents**

| Revision History                                        | 3      |

|---------------------------------------------------------|--------|

| Table of Contents                                       | 4      |

| 1. Introduction                                         | 5      |

| 1.1 Product Overview                                    | 5      |

| 1.2 Block Diagram                                       | 5      |

| 1.3Specifications Table                                 | 6      |

| 1.3.1 General                                           | 6      |

| 1.3.2 WLAN                                              | 6      |

| 1.3.3 Operating Conditions                              | ,<br>7 |

| 2. Pin Definition                                       | 8      |

| 2.1 Pin Map                                             | 8      |

| 2.2 Pin Table                                           |        |

| 3. Electrical Characteristics                           |        |

| 3.1 Absolute Maximum Ratings                            | 11     |

| 3.2 Recommended Operating Conditions                    | 11     |

| 3.3 Digital IO Pin DC Characteristics                   | 11     |

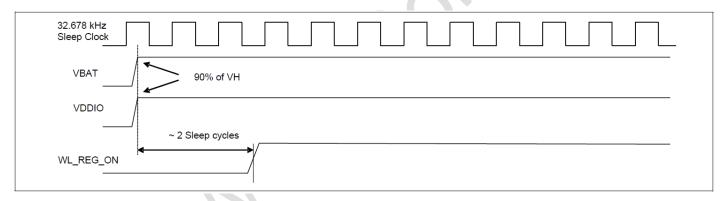

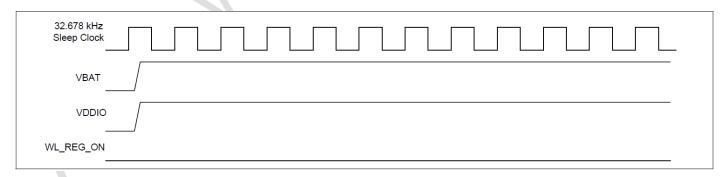

| 3.4 Power up Timing Sequence                            | 13     |

| 3.4.1 SDIO Host Interface Specification                 | 13     |

| 3.4.2 Sequencing of Reset and Regulator Control Signals | 15     |

| 3.5 Power Consumption*                                  | 16     |

| 3.5.1 WLAN                                              |        |

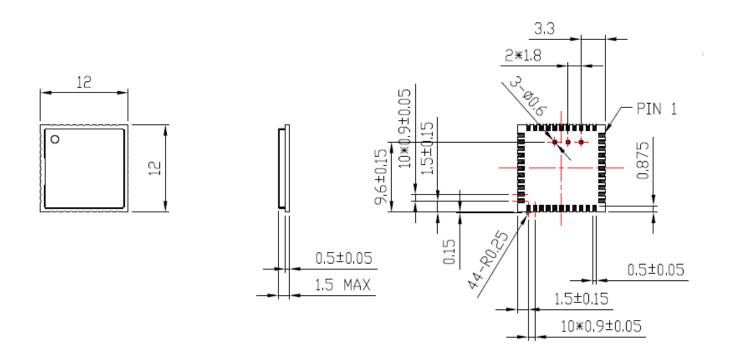

| 4. Mechanical Information                               | 17     |

| 4.1 Mechanical Drawing                                  | 17     |

| 5. Packaging Information                                | 18     |

#### 1. Introduction

#### 1.1 Product Overview

AzureWave Technologies, Inc. introduces the advanced IEEE 802.11 b/g/n WLAN module - AW-NM432SM. The module is targeted to mobile and embedded devices which need small footprint package, low power consumption, and multiple OS support. The module supports 2.4GHz IEEE 802.11b/g/n MAC/baseband/radio functionality. In addition, it also features an integrated Power Management Unit (PMU), Power Amplifiers (PAs), and a Low Noise Amplifier (LNA) to address the needs of mobile devices that require minimal power consumption and compact size. By using AW-NM432SM, the customers can easily enable the Wi-Fi embedded applications with the benefits of high design flexibility, short development cycle, and quick time-to-market. Specified in the IEEE 802.11 standard minimize the system power requirements by using AW-NM43SM. In addition to the support of WPA/WPA2 (personal) and WEP encryption, the AW-NM432SM also supports the IEEE 802.11i security standard through AES and TKIP acceleration hardware for faster data encryption. For the video, voice and multimedia applications the AW-NM432SM support 802.11e Quality of Service (QoS). The host interface is SDIO v2.0 interface.

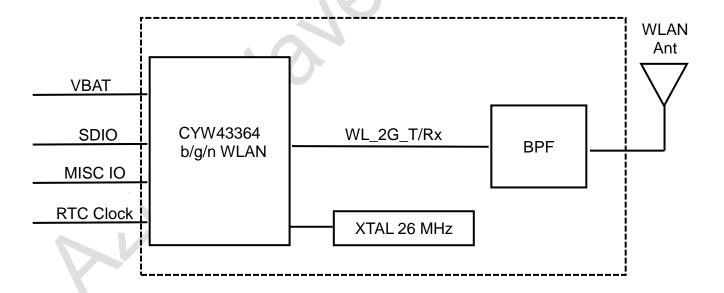

#### 1.2 Block Diagram

A simplified block diagram of the AW-NM432SM module is depicted in the figure below.

## 1.3 Specifications Table

#### 1.3.1 General

| Features            | Description                                 |

|---------------------|---------------------------------------------|

| Product Description | IEEE 802.11 b/g/n Wireless LAN Stamp Module |

| Major Chipset       | Cypress CYW43364                            |

| Host Interface      | WLAN: SDIO v2.0                             |

| Dimension           | 12.0mm(L) x 12.0mm(W) x 1.5 mm(H)           |

| Package             | 47 pin Stamp Module                         |

| Antenna             | 2.4G Ant: WiFi                              |

| Weight              | TBD                                         |

#### 1.3.2 WLAN

| Features                            | Description                                                                                                                                                                                                                  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLAN Standard                       | IEEE 802.11 b/g/n, Wi-Fi compliant                                                                                                                                                                                           |

| WLAN VID/PID                        | N/A                                                                                                                                                                                                                          |

| WLAN SVID/SPID                      | N/A                                                                                                                                                                                                                          |

| Frequency Rage                      | WLAN: 2.4 GHz                                                                                                                                                                                                                |

| Modulation                          | DSSS, OFDM, BPSK(9/6Mbps), QPSK(18/12Mbps), DBPSK(1Mbps), DQPSK(2Mbps), CCK(11/5.5Mbps), 16-QAM(36/24Mbps), 64-QAM (72.2/54/48Mbps)                                                                                          |

| Number of Channels                  | 802.11b: USA, Canada and Taiwan - 1 ~ 11 Most European Countries - 1 ~ 13 Japan - 1 ~ 14 802.11g: USA and Canada - 1 ~ 11 Most European Countries - 1 ~ 13 802.11n: USA and Canada - 1 ~ 11 Most European Countries - 1 ~ 13 |

| Output Power** (Board Level Limit)* | 2.4G                                                                                                                                                                                                                         |

|                      |                                                                                                                                                                                                                                                                                                             |           | Min | Тур | Max | Unit |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|-----|------|

|                      | 11b (11Mbps) @EVM<35%                                                                                                                                                                                                                                                                                       |           | 16  | 18  | 20  | dBm  |

|                      | 11g (54Mbps) @EVM \( \)                                                                                                                                                                                                                                                                                     | ≦-25 dB   | 14  | 16  | 18  | dBm  |

|                      | 11n (HT20 MCS7) @E                                                                                                                                                                                                                                                                                          | VM≦-28 dB | 13  | 15  | 17  | dBm  |

|                      | 2.4G                                                                                                                                                                                                                                                                                                        |           |     |     |     |      |

|                      |                                                                                                                                                                                                                                                                                                             | Min       | Тур | Max | U   | nit  |

| Receiver Sensitivity | 11b (11Mbps)                                                                                                                                                                                                                                                                                                |           | -89 | -86 | dE  | 3m   |

|                      | 11g (54Mbps)                                                                                                                                                                                                                                                                                                |           | -75 | -71 | dE  | 3m   |

|                      | 11n (HT20 MCS7)                                                                                                                                                                                                                                                                                             |           | -73 | -69 | dE  | 3m   |

| Data Rate            | 802.11b: 1, 2, 5.5, 11Mbps<br>802.11g: 6, 9, 12, 18, 24, 36, 48, 54Mbps<br>802.11n:MCS 0~7 HT20                                                                                                                                                                                                             |           |     |     |     |      |

| Security             | <ul> <li>WPA™- and WPA2™- (Personal) support for powerful encryption and authentication</li> <li>AES in WLAN hardware for faster data encryption and IEEE802.11i compatibility</li> <li>Cisco Compatible Extensions(CCX, CCX 2.0, CCX 3.0, CCX 4.0 CCX 5.0)</li> <li>Wi-Fi Protected Setup (WPS)</li> </ul> |           |     |     |     |      |

# \* If you have any certification questions about output power please contact FAE directly.1.3.3 Operating Conditions

| Features              | Description                                            |

|-----------------------|--------------------------------------------------------|

| Operating Conditions  |                                                        |

| Voltage               | Input supply for host I/O: 3.3V                        |

| Operating Temperature | -30~70 °C (Optimal RF performance guarantee -10~55 °C) |

| Operating Humidity    | Less than 85%R.H.                                      |

| Storage Temperature   | -40~85 °C                                              |

| Storage Humidity      | Less than 60%R.H.                                      |

| ESD Protection        |                                                        |

| Human Body Model      | 1.25KV                                                 |

| Changed Device Model  | 300V                                                   |

#### 2. Pin Definition

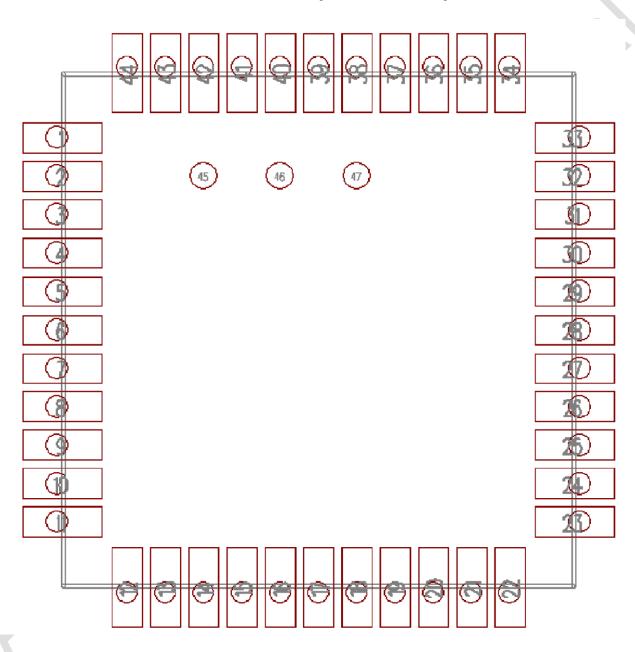

#### 2.1 Pin Map

#### AW-NM432SM Top View Pin Map

#### 2.2 Pin Table

| Pin No | Definition        | Basic Description                                | Voltage  | Туре            |

|--------|-------------------|--------------------------------------------------|----------|-----------------|

| 1      | GND               | Ground.                                          |          | GND             |

| 2      | WL_BT_ANT         | WLAN/BT RF TX/RX path.                           |          | RF              |

| 3      | GND               | Ground.                                          |          | GND             |

| 4      | NC                | Floating Pin, No connect to anything             |          | <b>Floating</b> |

| 5      | NC                | Floating Pin, No connect to anything             |          | Floating        |

| 6      | NC                | Floating Pin, No connect to anything             |          | Floating        |

| 7      | NC                | Floating Pin, No connect to anything             |          | <b>Floating</b> |

| 8      | NC                | Floating Pin, No connect to anything             |          | <b>Floating</b> |

| 9      | VBAT              | 3.3V power pin                                   | 3.3V     | VCC             |

| 10     | NC                | Floating Pin, No connect to anything.            |          | <b>Floating</b> |

| 11     | NC                | Floating Pin, No connect to anything.            |          | <b>Floating</b> |

|        |                   | Used by PMU to power up or power down the        |          |                 |

|        |                   | internal regulators used by the WLAN section.    |          |                 |

| 12     | WL_REG_ON         | Also, when deasserted, this pin holds the WLAN   | VDDIO    | I               |

| -      | WE_KEG_6H         | section in reset. This pin has an internal 200k  | 10010    | •               |

|        |                   | ohm pull down resistor that is enabled by        |          |                 |

|        |                   | default. It can be disabled through programming. |          |                 |

| 13     | WL_HOST_WAK<br>E  | WL Host Wake                                     | VDDIO    | 0               |

| 14     | SDIO_DATA2        | SDIO Data Line 2                                 | VDDIO    | I/O             |

| 15     | SDIO_DATA3        | SDIO Data Line 3                                 | VDDIO    | I/O             |

| 16     | SDIO_DATA_CM<br>D | SDIO Command Input                               | VDDIO    | I/O             |

| 17     | SDIO_DATA_CL<br>K | SDIO Clock Input                                 | VDDIO    | ı               |

| 18     | SDIO DATA0        | SDIO Data Line 0                                 | VDDIO    | I/O             |

| 19     | SDIO DATA1        | SDIO Data Line 1                                 | VDDIO    | I/O             |

| 20     | GND               | Ground.                                          |          | GND             |

| 21     | VIN LDO OUT       | Internal Buck 1.2V voltage generation pin        | 1.4V     | 0               |

| 22     | VDDIO             | 1.8V-3.3V VDDIO supply for WLAN and BT           | VDDIO    | VCC             |

| 23     | VIN_LDO           | Internal Buck 1.2V voltage generation pin        | 1.4V     | Ī               |

| 24     | LPO               | External 32K or RTC clock                        | 0.2~3.3V |                 |

| 25     | NC                | Floating Pin, No connect to anything.            |          | Floating        |

| 26     | NC                | Floating Pin, No connect to anything.            |          | Floating        |

| 27     | NC                | Floating Pin, No connect to anything.            |          | Floating        |

| 28     | NC                | Floating Pin, No connect to anything.            |          | Floating        |

| 29     | NC                | Floating Pin, No connect to anything.            |          | Floating        |

| 30     | NC                | Floating Pin, No connect to anything.            |          | Floating        |

| 31     | GND               | Ground.                                          |          | GND             |

| 32     | NC                | Floating Pin, No connect to anything.            |          | Floating        |

| 33     | GND               | Ground.                                          |          | GND             |

| -      |                   |                                                  |          |                 |

| 34 | NC    | Floating Pin, No connect to anything.         |       | <b>Floating</b> |

|----|-------|-----------------------------------------------|-------|-----------------|

| 35 | NC    | Floating Pin, No connect to anything.         |       | Floating        |

| 36 | GND   | Ground.                                       |       | GND             |

| 37 | NC    | Floating Pin, No connect to anything.         |       | <b>Floating</b> |

| 38 | NC    | Floating Pin, No connect to anything.         |       | Floating        |

| 39 | GPIO2 | Wi-Fi Co-existence pin with LTE(WLAN_SECI_RX) | VDDIO | ı               |

| 40 | GPIO1 | Wi-Fi Co-existence pin with LTE(WLAN_SECI_TX) | VDDIO | 0               |

| 41 | NC    | Floating Pin, No connect to anything.         |       | <b>Floating</b> |

| 42 | NC    | Floating Pin, No connect to anything.         |       | <b>Floating</b> |

| 43 | NC    | Floating Pin, No connect to anything.         |       | Floating        |

| 44 | NC    | Floating Pin, No connect to anything.         |       | Floating        |

| 45 | NC    | Floating Pin, No connect to anything.         |       | Floating        |

| 46 | NC    | Floating Pin, No connect to anything.         |       | Floating        |

| 47 | NC    | Floating Pin, No connect to anything.         |       | Floating        |

#### 3. Electrical Characteristics

#### 3.1 Absolute Maximum Ratings

| Symbol      | Parameter          | Minimum | Typical   | Maximum | Unit |

|-------------|--------------------|---------|-----------|---------|------|

| VBAT        | Power supply for   | -0.5    | -         | 6       | V    |

| VDDIO       | DC supply voltage  | -0.5    | -         | 3.9     | V    |

| VDDIO_RF    | supply voltage for | -0.5    | -         | 3.9     | V    |

| -           | DC input supply    | -0.5    | -         | 1.575   | V    |

| VDDRF       | DC supply voltage  | -0.5    | -         | 1.32    | V    |

| VDDC        | DC supply voltage  | -0.5    | -         | 1.32    | V    |

| Vundershoot | Maximum            | -       | -0.5      | -       | V    |

| Vovershoot  | Maximum overshoot  | -       | VDDIO+0.5 | -       | V    |

| Tj          | Maximum junction   | -<br>-  | 125       | -       | °C   |

a. Continuous operation at 6.0V is supported

#### 3.2 Recommended Operating Conditions

| Symbol | Parameter                               | Minimum | Typical | Maximum | Unit |

|--------|-----------------------------------------|---------|---------|---------|------|

| VBAT   | Power supply for<br>Internal Regulators | 3       | -       | 4.8     | V    |

<sup>\*</sup>The module is functional across this range of voltages. However, optimal RF performance specified in the data sheet is guaranteed only for 3.2V < VBAT <4.8V.

#### 3.3 Digital IO Pin DC Characteristics

| Symbol    | Parameter                                   | Minimum | Typical | Maximum | Unit |  |  |  |

|-----------|---------------------------------------------|---------|---------|---------|------|--|--|--|

| SDIO Inte | SDIO Interface I/O pins (For VDDIO_SD=1.8V) |         |         |         |      |  |  |  |

| VIH       | Input high voltage                          | 1.27    | -       | -       | V    |  |  |  |

| VIL       | Input low voltage                           | -       | -       | 0.58    | V    |  |  |  |

| VOH       | Output high voltage<br>@ 2 mA               | 1.40    | -       | -       | V    |  |  |  |

| VOL       | Output low voltage @ 2 mA                   | -       | -       | 0.45    | V    |  |  |  |

| For VDDI  | For VDDIO_SD = 3.3V:                        |         |         |         |      |  |  |  |

b. Duration not to exceed 25% of the duty cycle

| VIH      | Input high voltage                        | 0.625xVDDIO    | -     | -           | V  |

|----------|-------------------------------------------|----------------|-------|-------------|----|

| VIL      | Input low voltage                         | -              | -     | 0.25XVDDIO  | V  |

| VOH      | Output high voltage<br>@ 2 mA             | 0.75xVDDIO     | -     | -           | V  |

| VOL      | Output low voltage @ 2 mA                 | -              | -     | 0.125xVDDIO | V  |

| Other Di | Other Digital I/O Pins (For VDDIO = 1.8V) |                |       |             |    |

| VIH      | Input high voltage                        | 0.65xVDDIO     | -     | -           | V  |

| VIL      | Input low voltage                         | -              | -     | 0.35Xvddio  | V  |

| VOH      | Output high voltage<br>@ 2 mA             | VDDIO-0.45     | -     |             | V  |

| VOL      | Output low voltage @ 2 mA                 | -              | -     | 0.45        | V  |

| For VDD  | DIO = 3.3V:                               |                |       |             |    |

| VIH      | Input high voltage                        | 2.00           | -     | -           | V  |

| VIL      | Input low voltage                         | -              | -     | 0.80        | V  |

| VOH      | Output high voltage<br>@ 2 mA             | VDDIO-0.4      |       | -           | V  |

| VOL      | Output low voltage @ 2 mA                 | -10            | -     | 0.40        | V  |

| RF Swite | ch Control Output Pinsc (                 | For VDDIO_RF = | 3.3V) |             |    |

| VOH      | Output high voltage<br>@ 2 mA             | VDDIO-0.4      | -     | -           | V  |

| VOL      | Output low voltage @ 2 mA                 | -              | -     | 0.40        | V  |

| CIN      | Input capacitance                         | -              | -     | 5           | pF |

#### 3.4 Interface

#### 3.4.1 SDIO Host Interface Specification

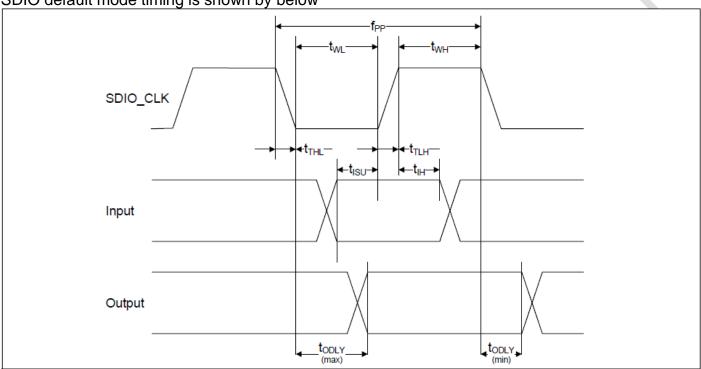

SDIO default mode timing is shown by below

SDIO Bus Timing (Default Mode)

| Parameter                                                          | Symbol | Minimum | Typical | Maximum | Unit |  |  |  |

|--------------------------------------------------------------------|--------|---------|---------|---------|------|--|--|--|

| SDIO CLK (All values are referred to minimum VIH and maximum VILb) |        |         |         |         |      |  |  |  |

| Frequency – Data Transfer mode                                     | fPP    | 0       | _       | 25      | MHz  |  |  |  |

| Frequency – Identification mode                                    | fOD    | 0       | -       | 400     | kHz  |  |  |  |

| Clock low time                                                     | tWL    | 10      | _       | _       | ns   |  |  |  |

| Clock high time                                                    | tWH    | 10      | _       | _       | ns   |  |  |  |

| Clock rise time                                                    | tTLH   | _       | -       | 10      | ns   |  |  |  |

| Clock low time                                                     | tTHL   | _       | _       | 10      | ns   |  |  |  |

| Inputs: CMD, DAT (referenced to CLK)                               |        |         |         |         |      |  |  |  |

| Input setup time                                                   | tISU   | 5       | I       | _       | ns   |  |  |  |

| Input hold time                                                    | tIH    | 5       | _       | _       | ns   |  |  |  |

| Outputs: CMD, DAT (referenced to CLK)                              |        |         |         |         |      |  |  |  |

| Output delay time – Data Transfer mode                             | tODLY  | 0       |         | 14      | ns   |  |  |  |

| Output delay time – Identification mode                            | tODLY  | 0       | _       | 50      | ns   |  |  |  |

SDIO Bus Timinga Parameters (Default Mode)

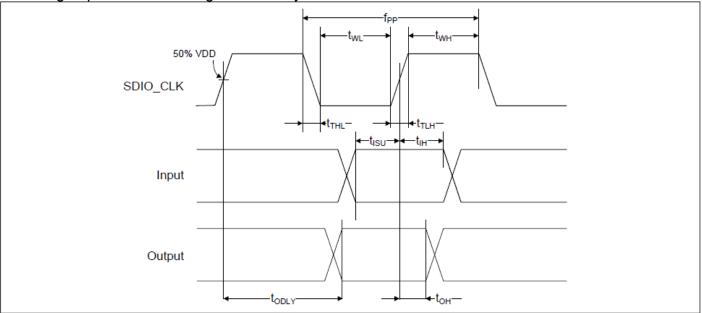

SDIO high-speed mode timing is shown by below

**SDIO Bus Timing (High-speed Mode)**

| SDIO Bus Timing (High-speed wode)                                  |        |         |         |         |      |  |  |  |

|--------------------------------------------------------------------|--------|---------|---------|---------|------|--|--|--|

| Parameter                                                          | Symbol | Minimum | Typical | Maximum | Unit |  |  |  |

| SDIO CLK (all values are referred to minimum VIH and maximum VILb) |        |         |         |         |      |  |  |  |

| Frequency – Data Transfer Mode                                     | fPP    | 0       | -       | 50      | MHz  |  |  |  |

| Frequency – Identification Mode                                    | fOD    | 0       | -       | 400     | kHz  |  |  |  |

| Clock low time                                                     | tWL    | 7       | -       | _       | ns   |  |  |  |

| Clock high time                                                    | tWH    | 7       | -       | _       | ns   |  |  |  |

| Clock rise time                                                    | tTLH   | _       | -       | 3       | ns   |  |  |  |

| Clock low time                                                     | tTHL   | _       | -       | 3       | ns   |  |  |  |

| Inputs: CMD, DAT (referenced to CLK)                               |        |         |         |         |      |  |  |  |

| Input setup Time                                                   | tISU   | 6       | -       | _       | ns   |  |  |  |

| Input hold Time                                                    | tlH    | 2       | -       | _       | ns   |  |  |  |

| Outputs: CMD, DAT (referenced to CLK)                              |        |         |         |         |      |  |  |  |

| Output delay time – Data Transfer Mode                             | tODLY  | _       | -       | 14      | ns   |  |  |  |

| Output hold time                                                   | tOH    | 2.5     |         | _       | ns   |  |  |  |

| Total system capacitance (each line)                               | CL     | _       |         | 40      | pF   |  |  |  |

**SDIO Bus Timinga Parameters (Default Mode)**

#### 3.4.2 Sequencing of Reset and Regulator Control Signals

The AW-NM432SM has three signals that allow the host to control power consumption by enabling or disabling the Bluetooth, WLAN, and internal regulator blocks. These signals are described below. Additionally, diagrams are provided to indicate proper sequencing of the signals for various operational states. The timing values indicated are minimum required values; longer delays are also acceptable.

#### Note:

The AW-NM432SM has an internal power-on reset (POR) circuit. The device will be held in reset for a maximum of 110 ms after VDDC and VDDIO have both passed the POR threshold. Wait at least 150 ms after VDDC and VDDIO are available before initiating SDIO accesses.

VBAT and VDDIO should not rise faster than 40 µs. VBAT should be up before or at the same time as VDDIO. VDDIO should not be present first or be held high before VBAT is high.

#### WLAN=ON

#### WLAN=OFF

#### 3.5 Power Consumption\*

#### 3.5.1 WLAN

|               | Item       |             |                      | VBAT=3.3V |      |           |         |      |  |

|---------------|------------|-------------|----------------------|-----------|------|-----------|---------|------|--|

| Band<br>(GHz) |            | BW<br>(MHz) | RF<br>Power<br>(dBm) | Transmit  |      |           | Receive |      |  |

|               | Mode       |             |                      | Max.      | Avg. | DUTY<br>% | Max.    | Avg. |  |

| 2.4           | 11b@1Mbps  | 20          | 17                   | TBD       | TBD  | TBD       | TBD     | TBD  |  |

|               | 11b@11Mbps | 20          | 17                   | TBD       | TBD  | TBD       | TBD     | TBD  |  |

|               | 11g@6Mbps  | 20          | 15                   | TBD       | TBD  | TBD       | TBD     | TBD  |  |

|               | 11g@54Mbps | 20          | 15                   | TBD       | TBD  | TBD       | TBD     | TBD  |  |

|               | 11n@MCS0   | 20          | 13                   | TBD       | TBD  | TBD       | TBD     | TBD  |  |

|               | 11n@MCS7   | 20          | 13                   | TBD       | TBD  | TBD       | TBD     | TBD  |  |

Current Unit: mA

<sup>\*</sup> The power consumption is based on Azurewave test environment, these data for reference only.

#### 4. Mechanical Information

#### 4.1 Mechanical Drawing

Tolerances unless otherwise specified + ±0.15mm

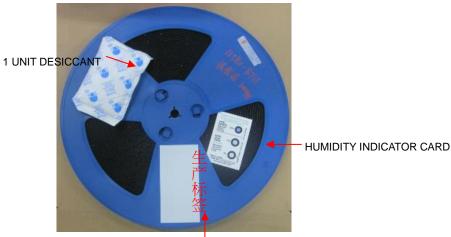

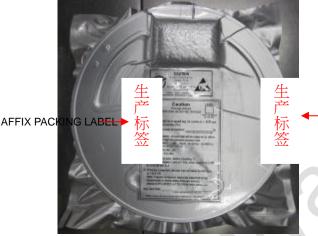

## 5. Packaging Information

#### 5.1

AFFIX PACKING LABEL

5.2

AFFIX PACKING LABEL

5.3

PINK BUBBLE WRAP

in whole or in part without prior written permission of AzureWave.

5.4

AFFIX PACKING LABEL

**5.5**1 Carton= 5 Boxes

AFFIX PACKING LABEL

in whole or in part without prior written permission of AzureWave.